# Welcome to 0510.7720.01 Winter semester 2021 Mixed Signal Electronic Circuits

Instructor: Dr. M. Moyal

Lecture 9 (after lect. 10/11) .....02/06/2021..

SUCCSSESIVE APROXIMATION ADC: Operation

**Design of Time Continuous SARs**

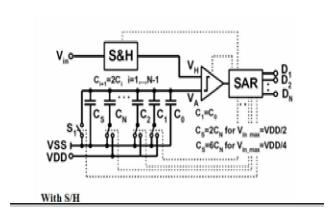

**Design of Switch C SAR**

**Error sources**

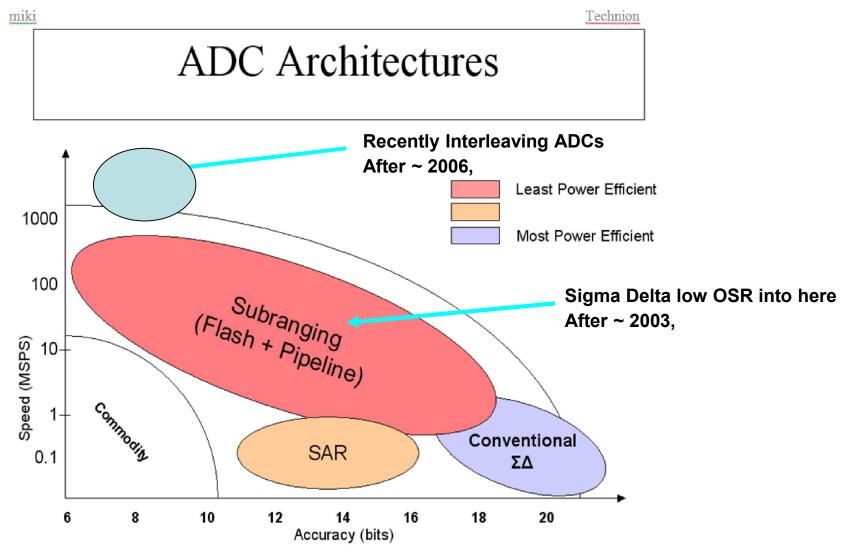

- □ ADC Architectures

- ☐ SAR ADCs

- ☐ Error Sources

#### A/D Converter ca. 1954

Figure 4.3: 1954 "DATRAC" 11-bit, 50-kSPS SAR ADC Designed by Bernard M. Gordon at EPSCO

B. Murman

#### **Common Data Acquisition Architectures**

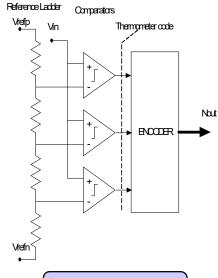

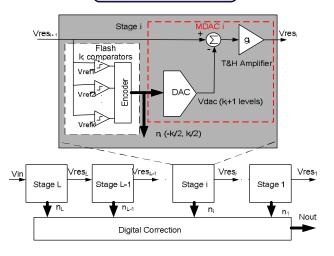

### FLASH ADC

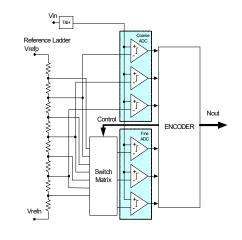

Sub ranging

SAR

TAU 05 Pipe Line

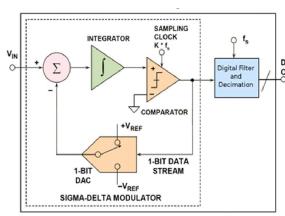

Sigma Delta

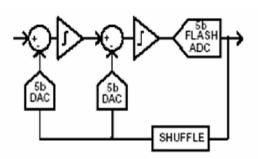

SD multi bits

Lect 09

#### Which ADC to use and why

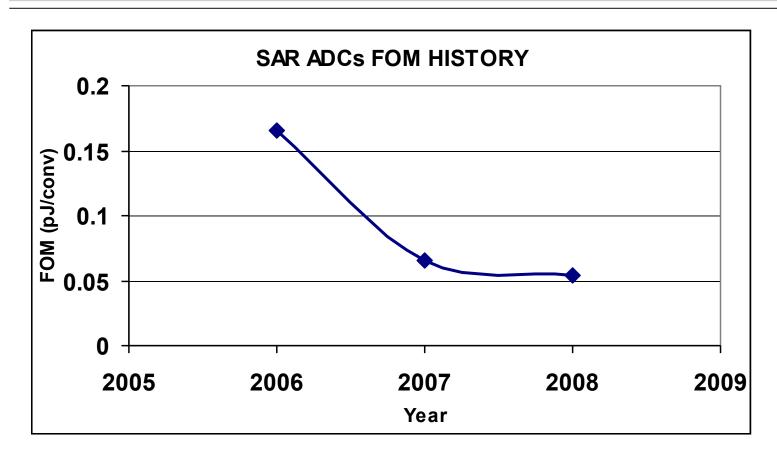

#### **SAR ADC FOM History**

2006 → 12b & 100Ks/s (180nm CMOS)

2007 → 9b & 50Ms/s (90nm CMOS)

2008 → 9b & 40Ms/s (90nm CMOS)

$$\frac{Energy}{Decision} = \frac{Power}{SamplingRate \times 2^{Nbit}}$$

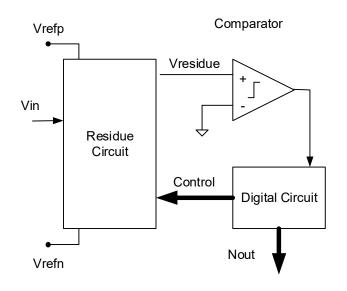

#### **Generic ADC:**

- $\Box$   $V_{residue}$  is a function of Vin Vref.

- ☐ The Residue sets the source of Linearity Errors

- ☐ The Comparator set the source Speed (Offset may be a problem )

- Must check always:

- ☐ Distortion (non linearity's) and ckt noise.

- Speed and Power

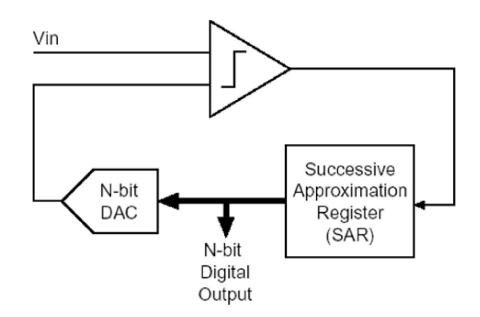

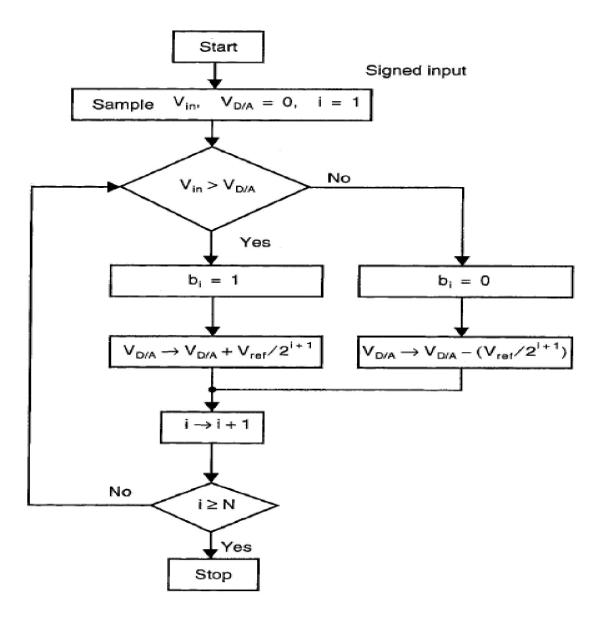

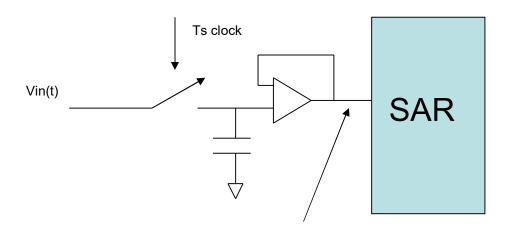

#### **Successive approximation ADC**

If Ts is twice maximum BW

And if N =desire bits

It requires minimum of p= N xTs passes to generate N bit

Output words limiting the through put

It requires N-bit accurate DAC

It requires faster settling elements

Strict timing is involved- transforming analog to digital each cycle

Comparator runs inside an open loop circuit therefore stability and closed loop Band width is not an issue.

### **SAR ADC – Timing**

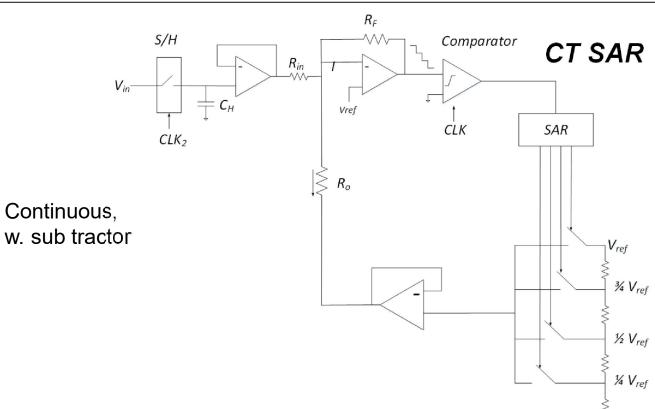

#### **SAR Operation/Design**

How to find RD value

$$R_D \gg \frac{V_{in\_max}}{R_{in}} = \frac{V_{ref}}{R_D}$$

$$R_D = \left[\frac{V_{in_F.scale}}{V_{ref}}\right]^{-1} R_{in}$$

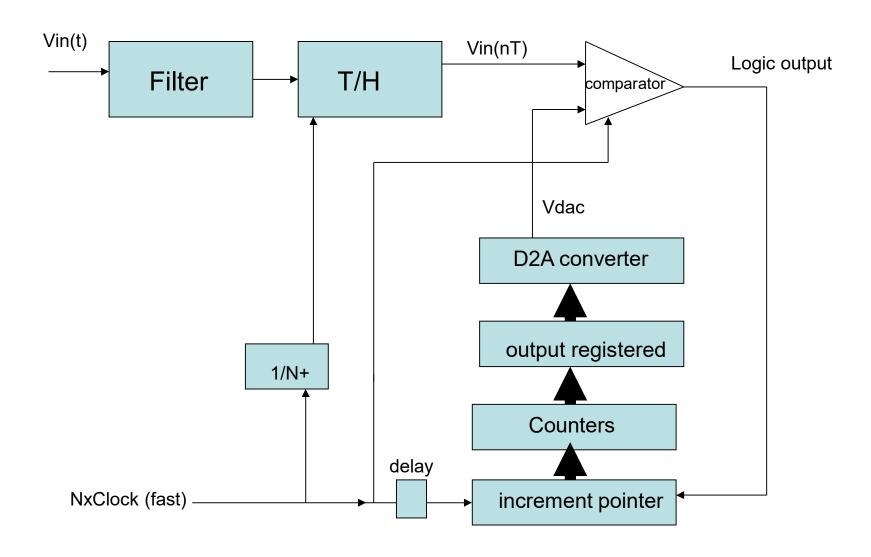

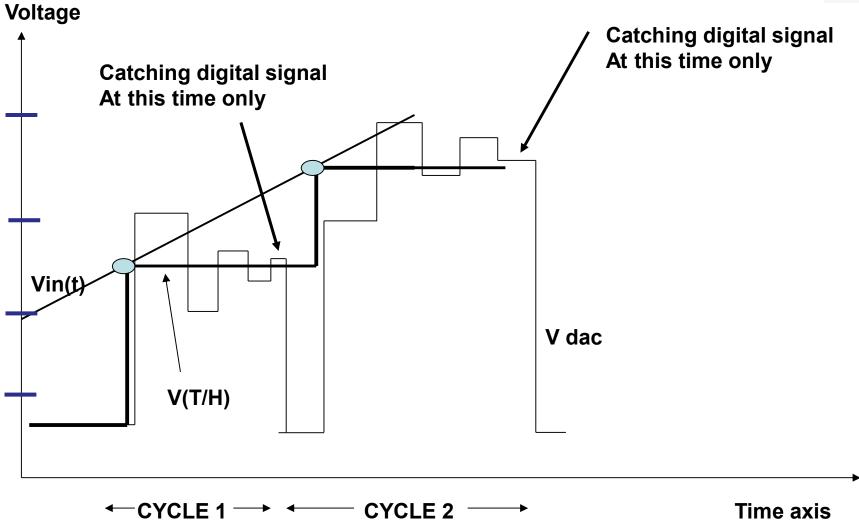

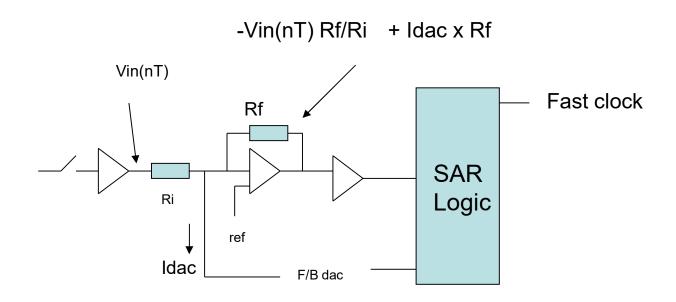

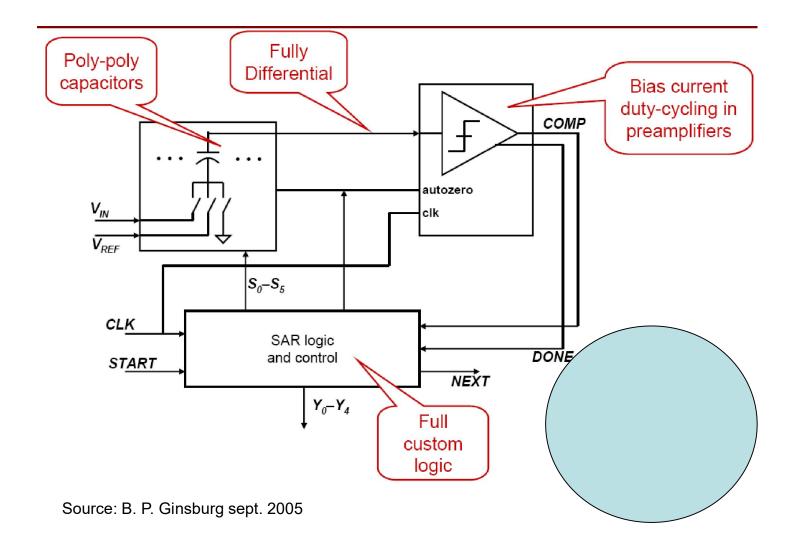

#### **Time Continuous SAR Block**

# ☐ 1<sup>st</sup> step sample and hold

Will be Covered later

- ☐ We know the errors,

- ☐ We know the speed needed

- ☐ We can proceed to build the block

□ 2<sup>nd</sup> step the sampled voltage part is being converted to I

Next how to build IDAC

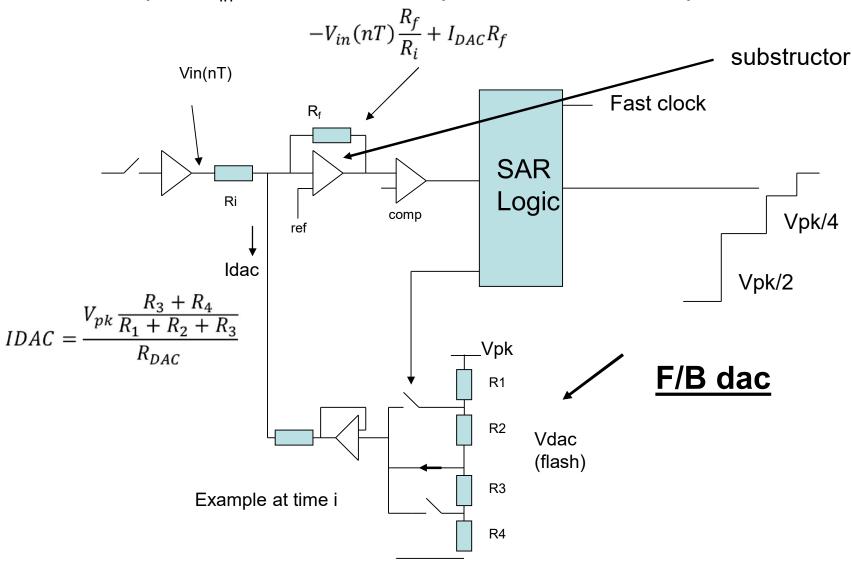

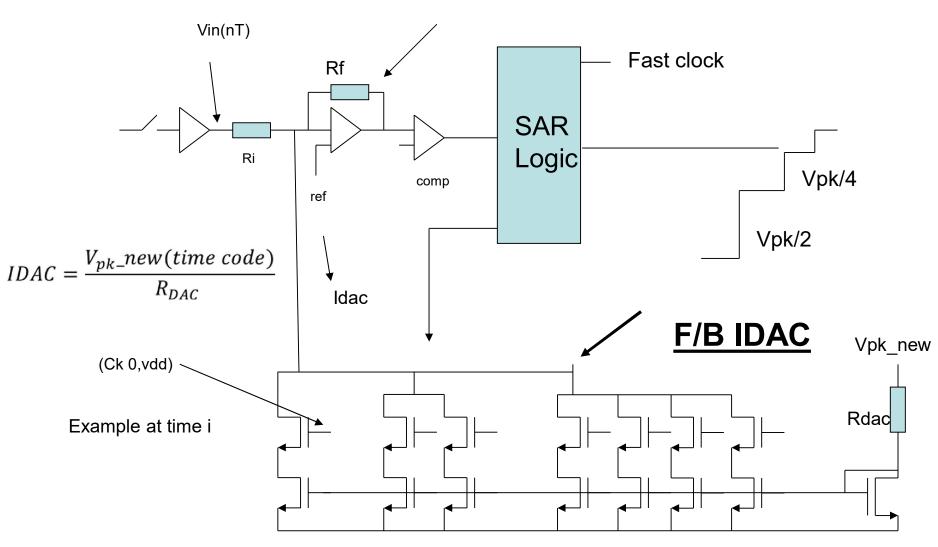

#### **SAR IDAC Feedback Generation**

☐ 3<sup>rd</sup> step the I<sub>in</sub> and IDAC is compared around the loop n times

#### SAR DAC - Use an Another Alternative to R-Ladder

- ☐ Go to DAC lecture pick another type?

- ☐ We got transistors they are small

- ☐ Current is always easy to generate with transistors

## SAR DAC – Another DAC – Speed and Area Improvement

$$-V_{in}(nT)\frac{R_f}{R_i} + I_{DAC}R_f$$

# SAR DAC – Another DAC – Speed and Area Improvement

| ☐ We used "not so efficient design"                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>□ Speed issues:</li> <li>□ BW amplifier,</li> <li>□ Subtraction with amplifier</li> <li>□ S/H - or Track and Hold.</li> <li>□ Area</li> </ul>               |

| <ul> <li>□ Can we do it other way?</li> <li>□ Lead to a simpler architecture</li> <li>□ No amplifiers!!</li> <li>□ With capacitors we can easily subtract</li> </ul> |

☐ Speed per cycle may be faster

# We want to generate

```

Vref/2.... 1st clock cycle

Vref/2 +/- Vref/4.. 2nd clock cycle

Vref/2 +/- Vref/4 +/-Vref/8 3rd clock cycle

Etc..., ,

```

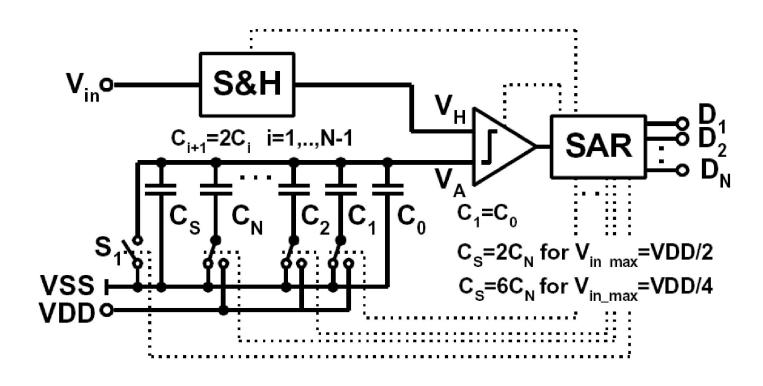

So lets use capacitor DAC to do this.

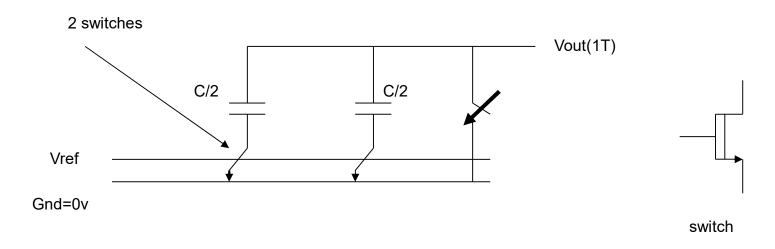

#### **Charge Distribution SAR DAC Operation**

Step 1.- clock n=1, reset everything to 0 point – "wasted state" but needed because capacitors plates are held at a "value" for DC

Vout = 0v all capcitors plates are shorted to 0 In reality after nRonC/2 time ( Ron=1/ucox(vgs-vt)(w/l)

#### Generate V<sub>ref</sub>/2 to Compare

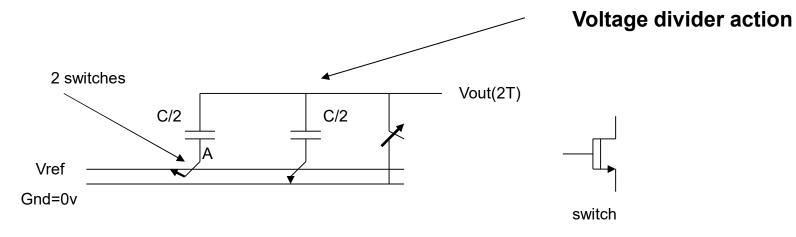

#### Step 2.- clock n=2, generate vref/2 to compare with input

Vout = 1/2vref at the end of the clock time

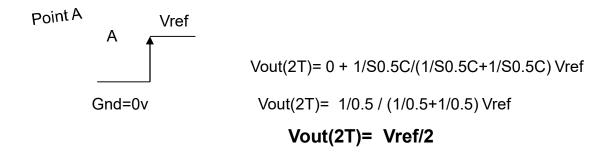

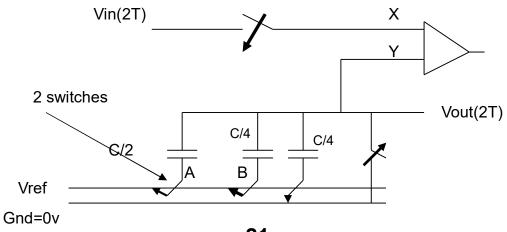

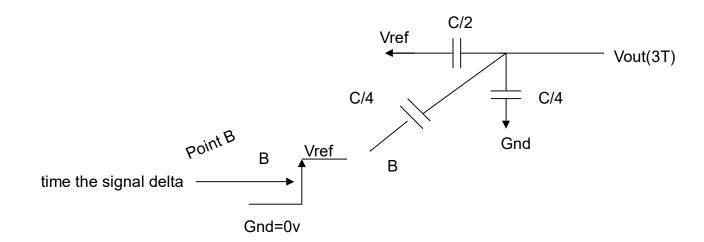

### Compare to $V_{ref}/2$ and Generate $V_{ref}/2 + V_{ref}/4$

in time = "3" add 1/4 vref

Re arrange C to units

TAU 0510.7720.01/2021 21 Lect 09

delVout(3T)= ( 0.25C / C ) Vref

Del Vout(3T)=1/4 (time the signal delta)

Vout(3T)= Vref(2T) + 1/4 Vref

Vout(3T)= Vref/2+Vref/4

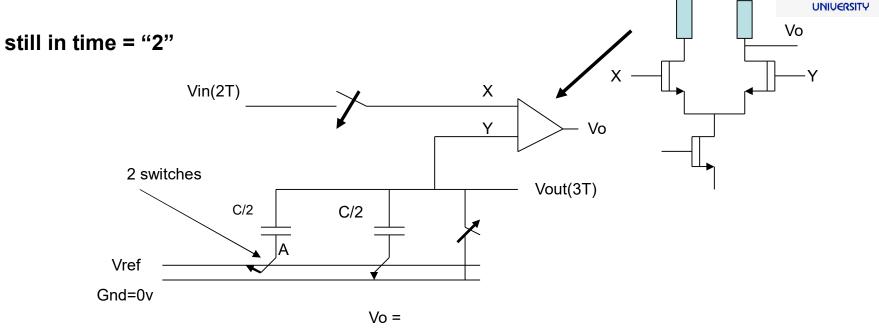

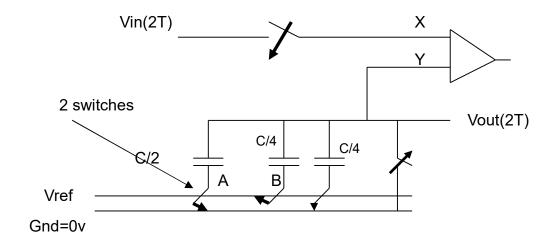

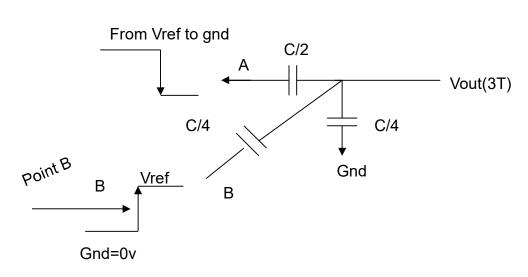

## Generate the Minus $\rightarrow$ $V_{ref}/2 - V_{ref}/4$

#### in time = "3" add $-\frac{1}{4}$ vref

#### 2 operations

delVout(3T)= -0.5+0.25 Vout(3T)= V(2T) + -0.5+0.25 delVout(3T)= 1/4Vref

#### Generate the Minus of the Input as well Easily

T=1

$$\frac{\text{Vout(1T)= Gnd=0v}}{\text{Vin}}$$

$\frac{\text{Gnd=0v}}{\text{Gnd=0v}}$

T=2

$$\frac{\text{Vout(2T)= 0-Vin}}{\text{Vin}}$$

$\frac{\text{Gnd=0v}}{\text{Gnd=0v}}$

And on.. And on.. Until the number of bits M+1

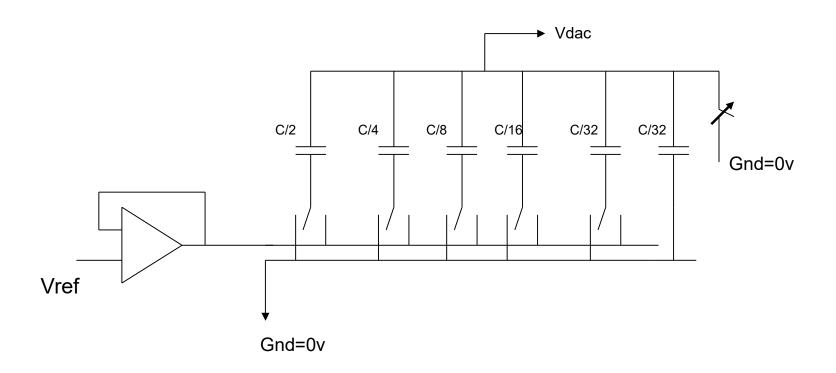

# .... Let's Look at Charges SAR

5bit dac

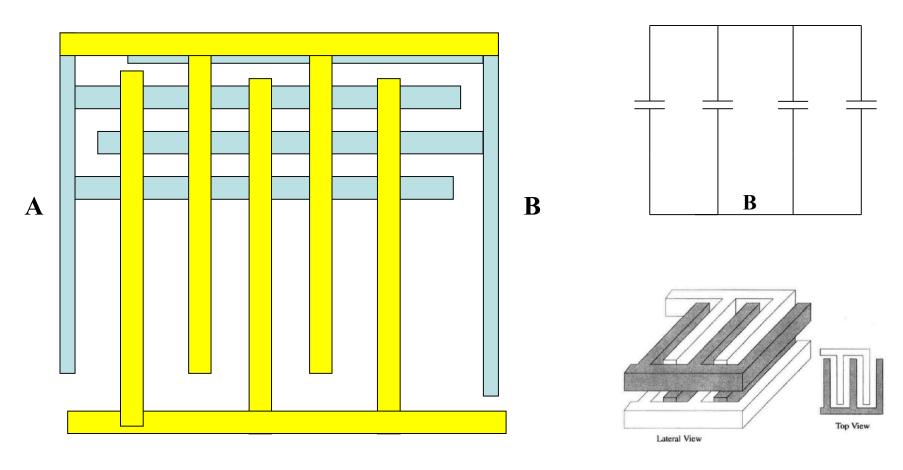

#### Fring. Caps to Improve Area Density (capacitors on IC)

$$C = C_o WL \longrightarrow C = C_o WL + 2C_{fr} (W + L)$$

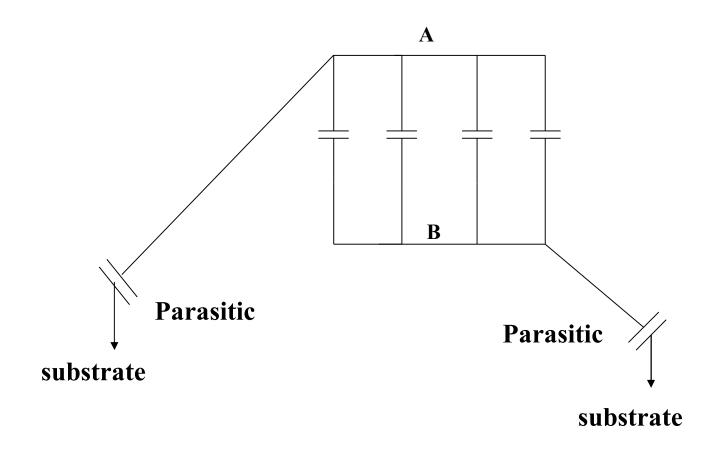

Accuracy in silicon is low ~ +/-20% Low temperature/V dependency Matched well. What about plate parasitic? TAU 0510.7720.01/2021

Co= 1-2 ff/uu if Metal to Metal sand witched With Fringing effect into the picture:

#### Fring. Capacitors-Parasitic Errors

C parasitic ~0.1-0.2C total! – how to design it out..

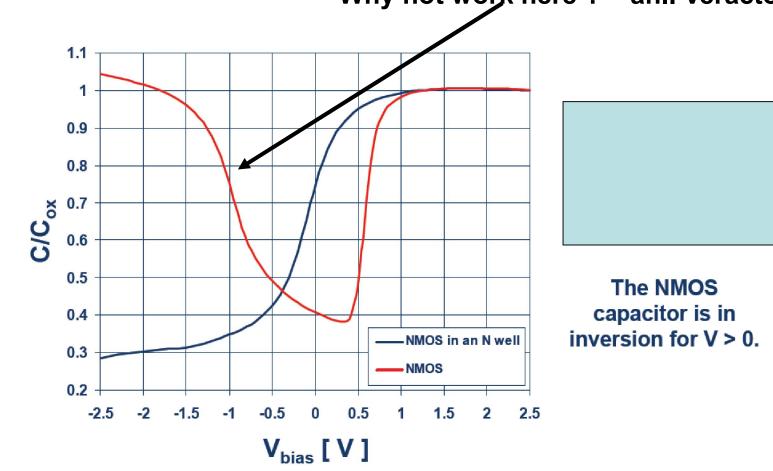

#### Silicon Transistors as Capacitors

A

# Capacitors from MOS (transistor)→triki.-watch the plates potential.

In accumulation (off)-----→ Vgs < Vt (n ch)

$$C = C_o W L$$

P can be in both

C=Cox

NMOS

Inversion Region

VAB

GND

p-substrate

Cap is to the drain sources!

Next to Vt – C drops to ~ 0.3 its max value

It's a voltage dependent capacitor –

doesn't work good with 0 volt across it (integrator and opamp)

#### **Silicon Transistors as Capacitors**

Giovanni Anelli, CERN

#### **Errors in SAR ADCs**

- ☐ Its an accurate structure

- ☐ Subtraction using caps

- ☐ Low/average power: SH, one comparator, DAC, and Logic

- □ 8b-200msps is possible

- ☐ But: Need Accuracy in the DAC.

- ☐ Comparator offset < ~ 0.5 LSB Easily calibrated

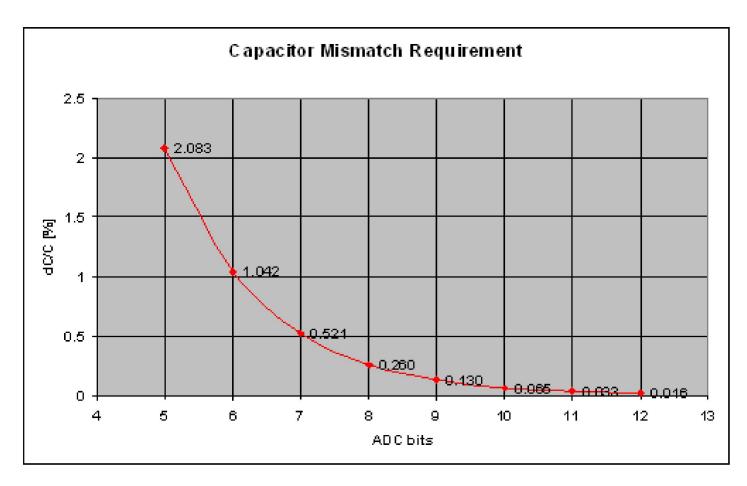

ACCURACY: FUNCTION OF DAC (CAPACITORS) MATCHING

#### **Matching**

$$C \approx \varepsilon \frac{WL}{t} \qquad \qquad \left(\frac{\Delta C}{C}\right)^2 = \left(\frac{\Delta \varepsilon_r}{\varepsilon_r}\right)^2 + \left(\frac{\Delta t_{ox}}{t_{ox}}\right)^2 + \left(\frac{\Delta L}{L}\right)^2 + \left(\frac{\Delta W}{W}\right)^2$$

- ☐ Once again can correlate to area with good accuracy

- ☐ How is it given

- 1. A\_deltaC/C is based on sigma of (deltaC / C) vs. 1/sqrt(WL) typ. number 2fF/micron square

#### To get to the best matched number you need to:

- Use identical geometries

- Use large unity capacitance (minimize fringing)

- Use common centroid arrangement

- Use dummy capacitors

- Use shielding

- Account for the connections' contribution.

- Don't run connections over capacitor

- Place capacitor in low stress areas

- Place capacitors far from power devices

#### An Example

# Find the LSB capacitor size (and total capacitors) for a 12b SAR ADC Given that 10ff unit match to 0.8%. (to 1 sigma)

$$C_{unit} = 10 fF \qquad \left(\frac{\Delta C}{C}\right)_{unit} = 0.8\%$$

$$\Delta_{noise} = \sqrt{\frac{\Delta^2}{12} + [Distortions]^2 + \frac{KT}{C_T}}$$

$$1pF \sim 64E^{-6} V / \sqrt{Hz}$$

Let give [Distortions]  $\gg \frac{1}{3} LSB$  wight

$$\left[\frac{\Delta C}{C}\right]_{Full\ Scale} = \frac{1}{3} \left[\frac{1}{2^n - 1}\right] = 0.0081\%$$

$$\left[\frac{\Delta C}{C}\right]_{LSB} = [0.0081]\sqrt{2^n - 1} = 0.518\%$$

$$C_{LSB} = [C_{unit}] \left[ \frac{0.8}{0.518} \right]^2 = 23.85 fF$$

$$C_{total} = 97.67pF$$

Not to influency the converter

$$C_{LSB} = \left[C_{unit}\right] \frac{\left[\left(\frac{\Delta C}{C}\right)_{Full\ scale} \sqrt{2^{n}-1}\right]^{2}}{\left[\left(\frac{\Delta C}{C}\right)_{unit}\right]^{2}}$$

### **Example of Matching Requirement on F. Scale (MSBs)**

2 to the n x 2/3 (2/3 only as example not to give all the error to the linearity)

#### How to Build One - What is Needed to Look for

#### **Word on the References**

References issues:

#### REFERENCE HOLDING BREF IS HARD TO DO:

During switching phase references has to settle every clock (fast) They are op amp driven therefore make the design almost as op-amp based

Also the comparator must settle every cycle. (faster)

#### Summary - C or R DAC

- Most time absolute value can move =+/-15% to +/-20% and does not significantly matter but ratio's do

- ☐ However, the bigger the area the better the matching

- ☐ Typical values 30ff can match 3-sigma to better ~ 0.5%

- ☐ Matching is area dependent generally by the root of (W x L)

- ☐ In SAR there is contradiction large is good for matching however speed is degraded a lot R switch x C and its multiplied N bit for a complete cycle.

#### **Power / Analog Components**

- ☐ Without amplifiers power is set by S/H, References, 1 comparator, and digital blocks+clocks

- ☐ Generally for lower number of bits logic may be significant

- ☐ Area. For many bits analog set the power waist.

- ☐ Logic running multiple times for each conversion and capacitor size (forcing a large drive current)

- ☐ Power waist : S/H + Comparator + Reference + Switching/logic

#### Good:

- ☐ Lowest possible power- FOM

- ☐ Fewer analog elements,

- ☐ T/H or S/H drive low capacitance

### **SAR- Key Points**

| The Feed Back ADC (SAR) offers significant hardware savings compared to flash ADCs because the coarse Quantizer (comparator) resolution m can be much smaller then the converter resolution. N                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>However, its suffer from drawbacks making it not suitable for many applications because:</li> <li>□ It requires p= N/m passes to generate N bit output words limiting the through put</li> <li>□ It requires N: bit accurate DAC</li> </ul> |

□ So, if speed is a problem should we combine SARs in time ??

☐ It requires faster settling elements

■ but No need amplifiers!

# **End Lecture 9**