Welcome to 046188 Winter semester 2012 <u>Mixed Signal Electronic Circuits</u>

Instructor: Dr. M. Moyal

Lecture 5 (part b)

FLASH ADC Design with error sources.

www.gigalogchip.com

## "Error list"

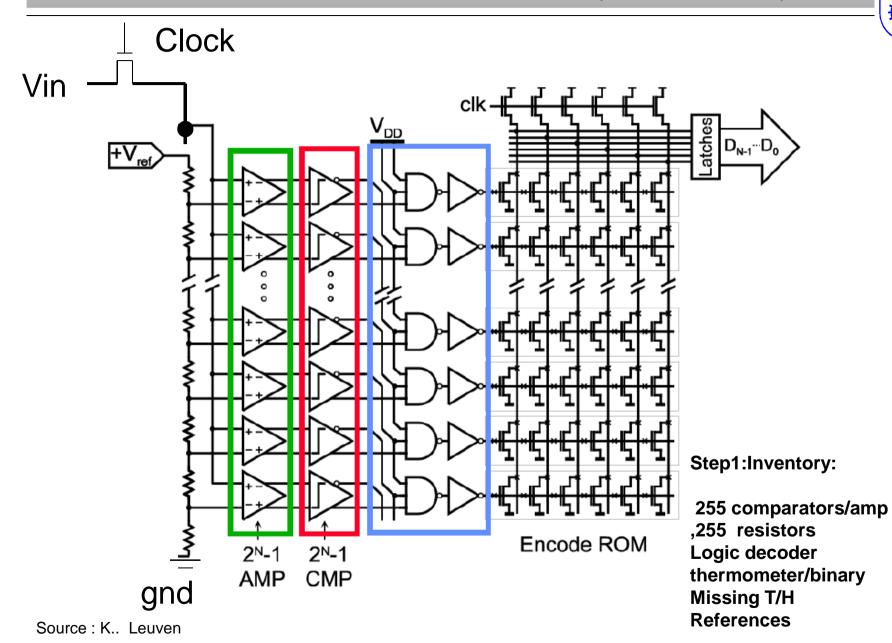

## Flash ADC – Design and Error Sources

#### ENOB= (SNDR - 1.76) / 6.02

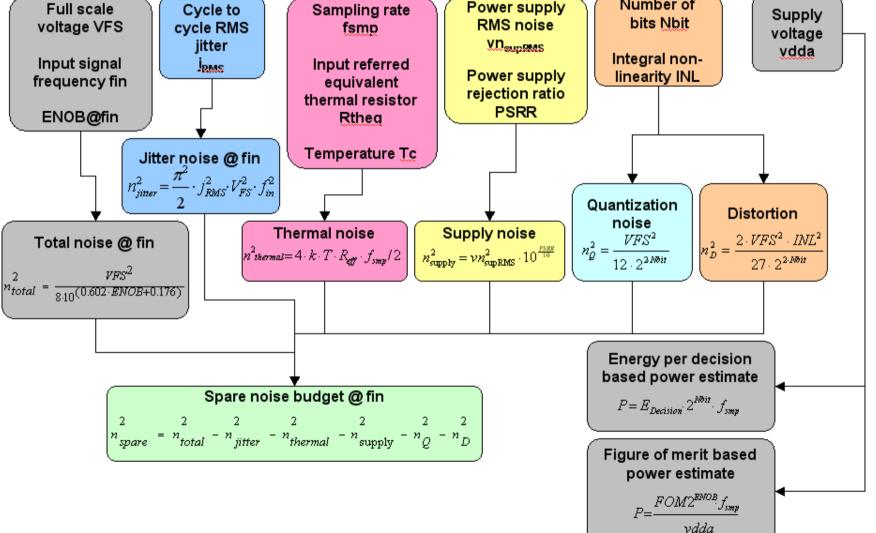

Green – Flash Red - Pipe line Blue Folding Pink Open Loop Pipe line Sigma delta ADC ? (0-200MHz, 9-14bit)

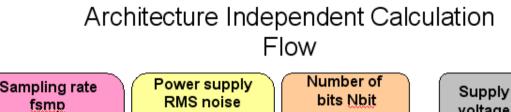

# SNRD (AC) Measured Converter S/N N quantization D Distortions

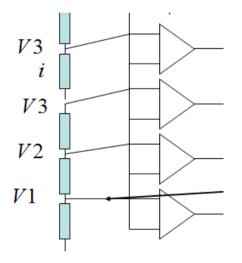

Comparator Offset Resistor mismatches Power Speed limit first stage Signal Feed through Gain Dynamic Range – Max Vref Comparator Meta stability (and speed) Following stages – (bubbles) Clock distribution

A good way to see the errors lets go over flash design

## An 8 bits Flash ADC

*Kn* =µ*Cox*

### **Step 2:** Design the converter: (w/l) with correct accuracy:

Find/look for:

Accuracy: where in the design non linearties is created 1) Comparator offsets – random mechanism 2) Resistor ladder – random

gnd

V

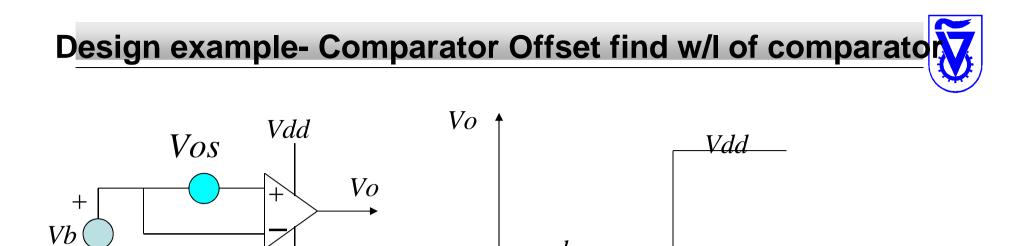

Vos

Offset- at what voltage (X-Y) the comparator switch

gnd

gnd

#### **Comparator Offset**

X

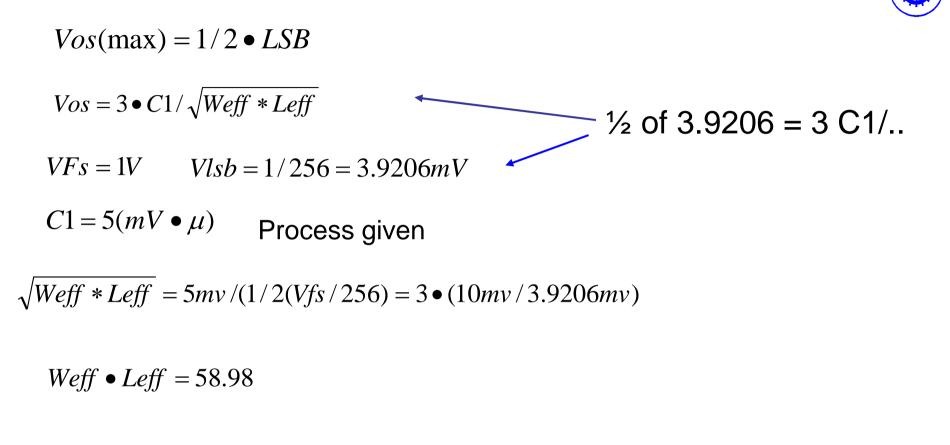

Given process 180nm is C1

$C1 = 5(mV \bullet \mu)$

And we use the equation from lect4-5.

$\sigma(\Delta Vt) = C1/\sqrt{Weff * Leff}$

But now we need 3 sigma's - so "no" error is created - yield

$Vos \leq 3 \bullet \sigma(\Delta Vt)$

Remember: Could be the biggest problem: bad for low voltage technologies

Technion 046188/2012

#### **8bit-Comparator Offset calculations cont.**

Implies L=0.18um W=327um

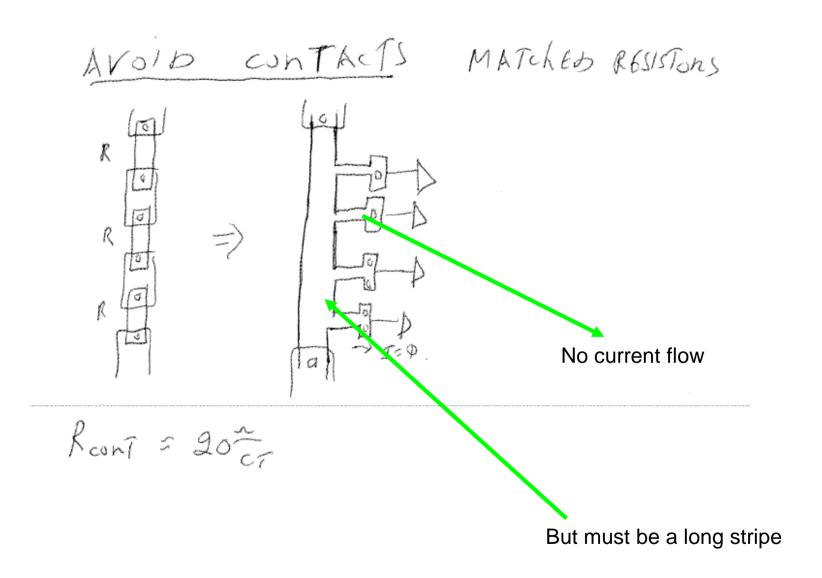

## **LADDER MISMATCHES-** length determinations

#### **Get rid of Contact errors**

## Step 3. power dissipation

For Kn=60e-6, I=0.18u w=327un, and if Vgs-Vt=0.1

$Ids = \mu Cox(W/2L)(Vgs-Vth) \times (Vgs-Vth) \times (255) = 541uA \times 255$  $= \sim 138mA$

*P*= *Without T/H, logic, clock, resistor ladder we re at* **248mW**

assuming Remember <78mV we are not in sat.

•Should we increase L ? (keep wxl , drop Power ?)

•Should we check real speed to get I

•Should we calibrate offset and not increase w/l?

Stop and re think: Isn't power based on I, shouldn't we look at speed first ? For min I

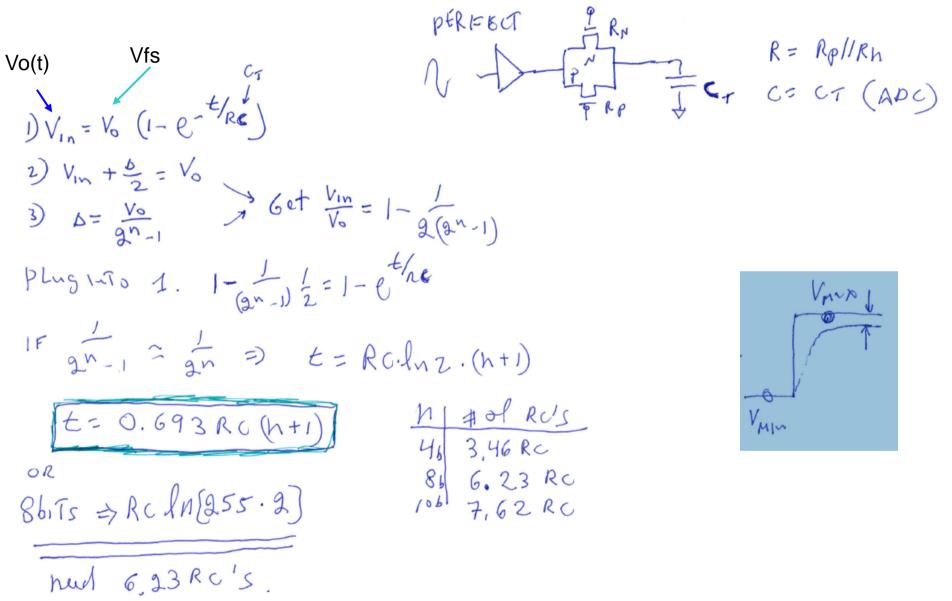

## **Step 4.** Meet speed limits

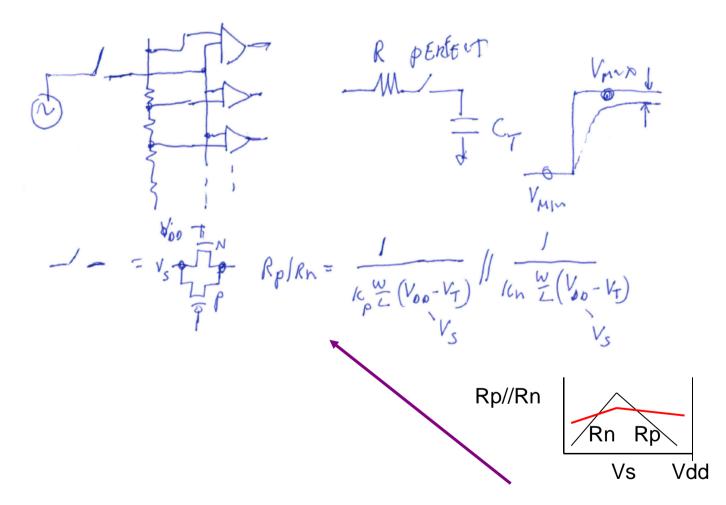

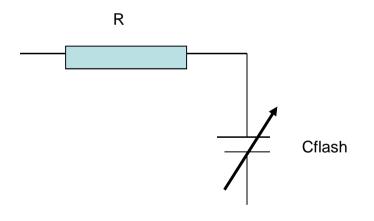

#### Speed limit due to front stage.- Model

Cin is so large that Rin is important

#### Speed limit due to front stage.- Acquisition time

Technion 046188/2012

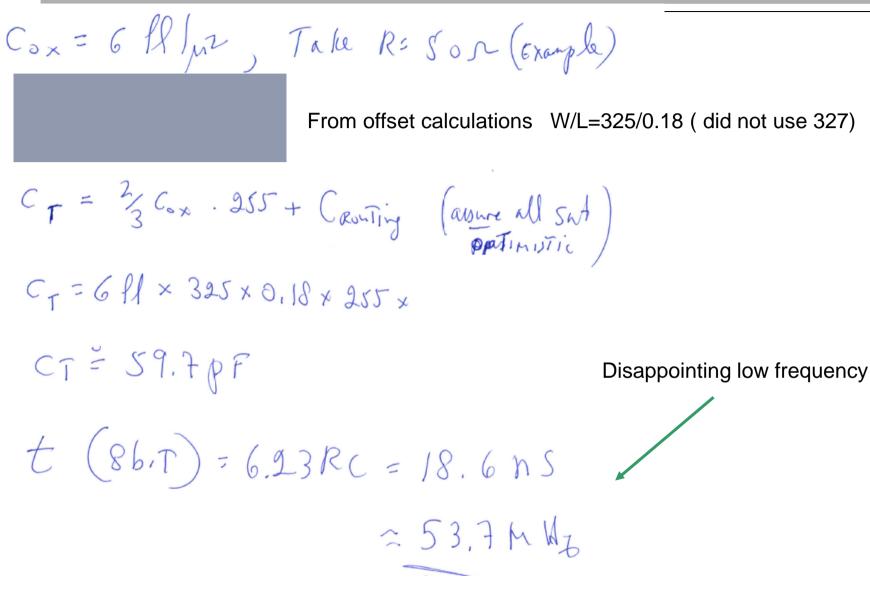

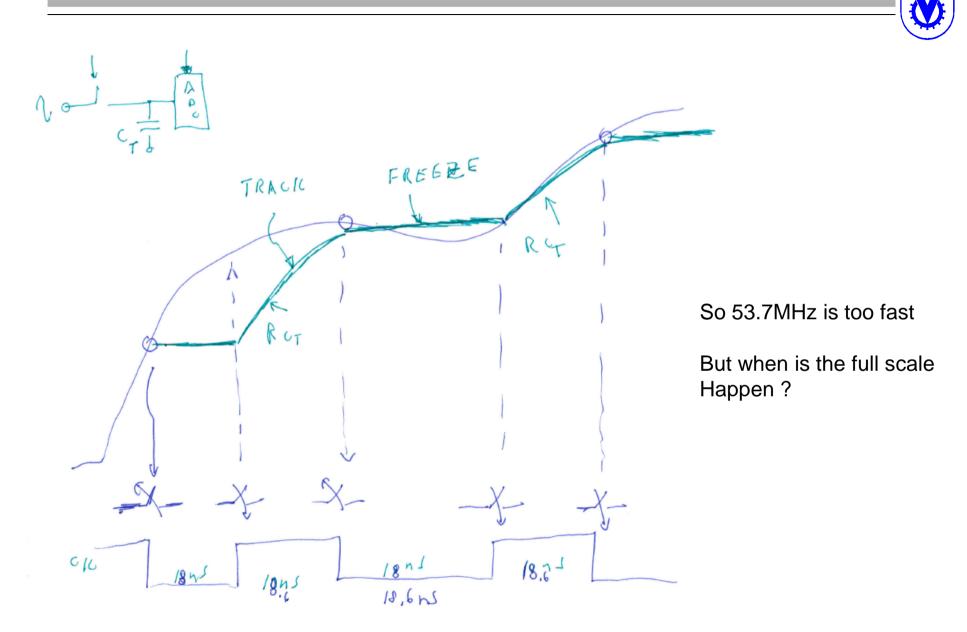

#### **Speed limit due to front stage- Calculation**

Stop and re think: New buffer to drive low cap ? Re look at matching – calibrate to reduce Ct ? Lect 05

#### Speed limit due to front stage.- view

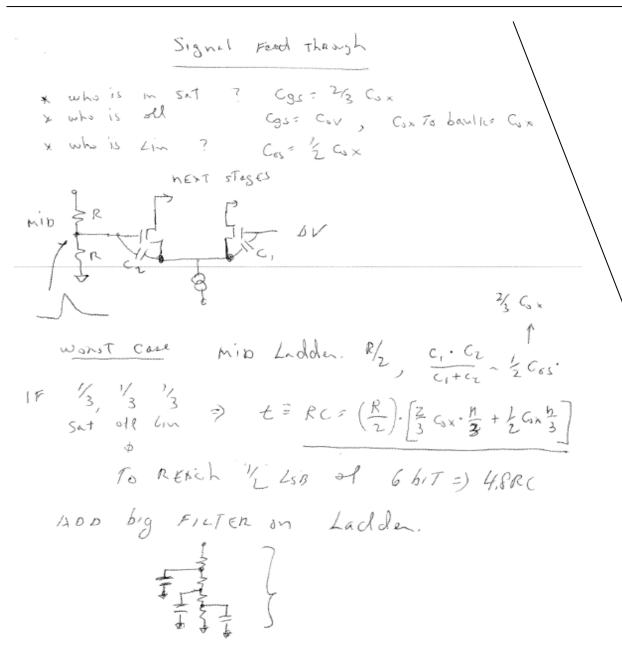

#### **Speed limit: Feed through speed**

$$\frac{V_{mid}}{V_{in}} = \frac{\pi}{4} \cdot f_{in} \cdot R_{ladder} \cdot C$$

Source : Esscirc 2002. Leuven

C total capacitance Find max input ladder R. for no effect on feed through

(After matching calculations are satisified).

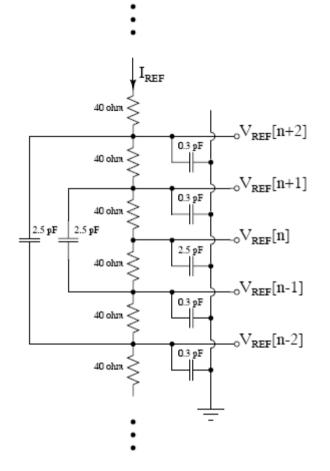

#### **Example removed feed through effect.**

**Example: Cap stabilization 5b 1GS.s flash** Source: Esscirc 2006 Helsinki univ, Olli Viitala

## Step 5. Spec the needed comparator

#### **Comparator Gain- more in comparator design**

Corp Gain 100 analog v L L Port OVIN LSB 10 need enough Gain  $() \delta V = V_1 - V_2 = \frac{1}{10} LSB$ Vos= 1.8V, nb.J.  $A_{ol} = \frac{1.8V}{\frac{Vrs}{2n}} \cdot 10 = \frac{18}{\frac{0.5}{28}} = 18 \cdot 2^3 = 9216 = 79 da$ 8 bit  $\int \frac{0.5}{28} = 18 \cdot 2^3 = 9216 = 79 da$ 8 bit one on 2 stages with enough More details in 2 É SPEEO? comparator design 3 Let cruate a Latch on posiTive Gain The rest of the dy There goon V not to get !

Technion 046188/2012

| capacitors  | Saturation | Linear     | Off       |

|-------------|------------|------------|-----------|

| C gate to S | 2/3Cox+Cov | 1/2Cox+Cov | Cov       |

| C gate to D | Cov        | 1/2Cox+Cov | Cov       |

| C gate to B | 0          | 0          | Cox//Ccb+ |

$$HD_2 = \frac{V_O \omega C_1 R}{2\sqrt{1 + (2\omega C_0 R)^2}}$$

Source : Esscirc 2002 Leuven

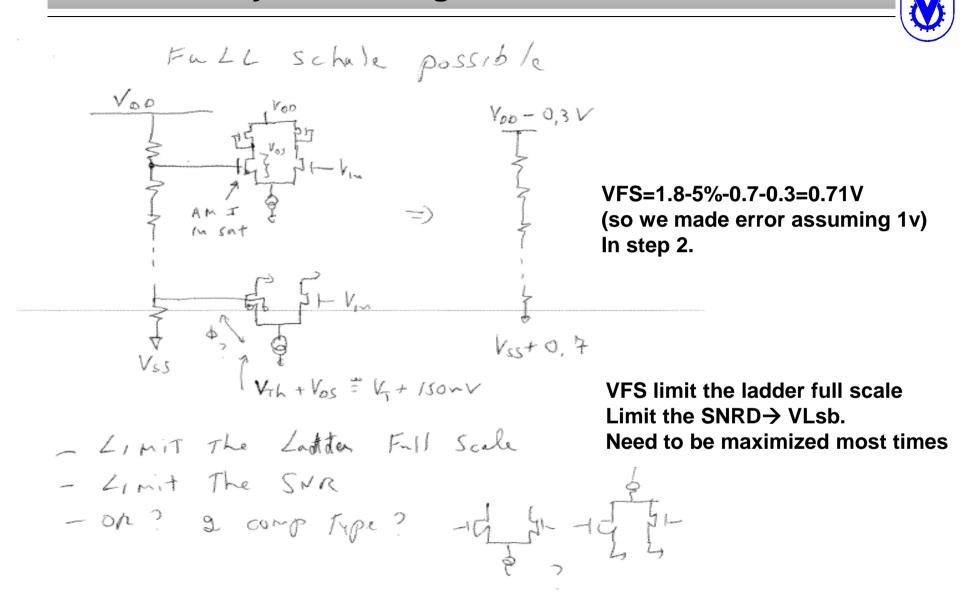

## Step 6. Set the maximum dynamic range

#### **Dynamic Range – Max Vref**

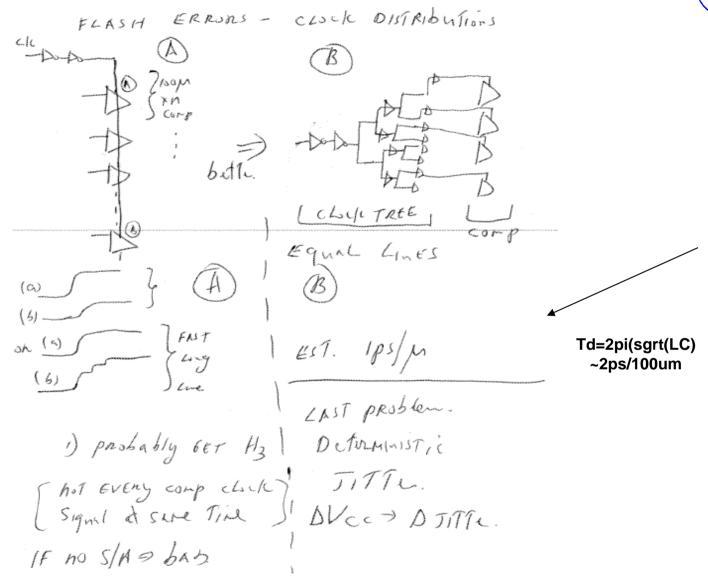

#### **Step 7.** Clock- jitter requirement set requirements

#### FLASH CLOCK DISTRIBUTION ERRORS

#### Step 8. Digital design – can we help the analog ? What can we do there..

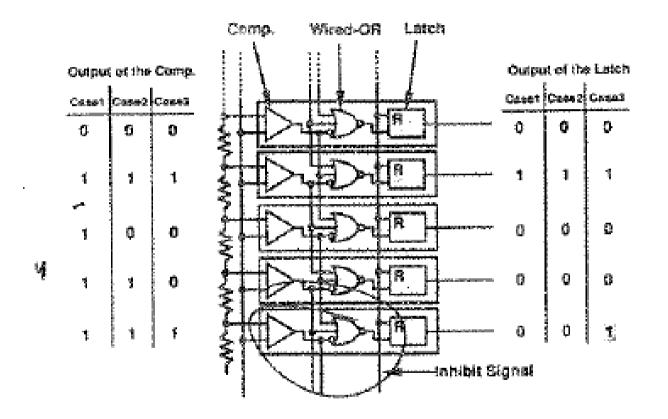

#### **Error Correction**

#### Bubble error look at your neighbour Won't correct two errors

# Since nothing worked well .. (FOM = 17 is high $\rightarrow$ 10to12 x 248mw / (57e6X255)

How about other architectures..

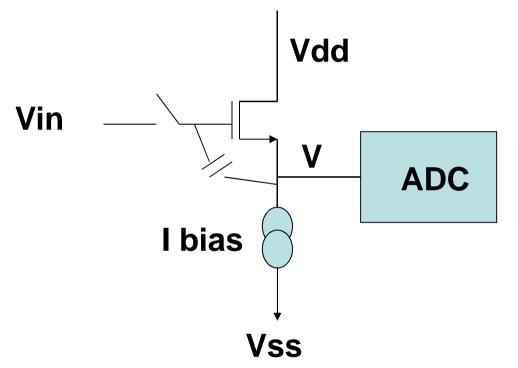

Why does this circuit reduces capacitance of T/H and help drive the large capacitance of the ADC ?

## End lecture 05b