Welcome to 046188 Winter semester 2012 <u>Mixed Signal Electronic Circuits</u>

Instructor: Dr. M. Moyal

## Lecture 11- Synthesis, and design..

### **Over Sampling ADCs**

Example of 1 loop design – time continuous Stability of higher loops Switch C building blocks Synthesis Switch C Time continuous - design

www.gigalogchip.com

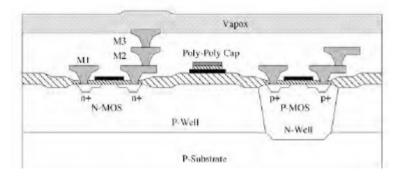

### **CMOS** technology

#### Symbols of the MOS transistors

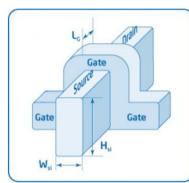

#### Intel's 22nm Process. Atom, ARM, Apple

| by Paul McLel | llan       |          |  |

|---------------|------------|----------|--|

| Published on  | 05-05-2011 | 06:52 AM |  |

olid nd om d

so eon

iness ) run

I's m the

Intel had a big press event yesterday at which they announced details of their 22nm process. In a change from their current processes, it goes with a vertical gate. In fact 3 gates which gives them much better control of leakage through transistors that are switched off, along with more transmission through the on transistors. They claim to get 37% better performance and 50% power reduction compared to 32nm. Although vertical transistors have been talked about for nearly a decade, Intel's tri-gate is the first time anyone has brought them into volume production.

One speculation is whether the performance of Atom at 22nm hits a better power/performance than ARM does at 28nm in TSMC and other foundries. Of course the ATOM vs ARM battle isn't really just about technical specs but rather about ecosystems and partners. The mobile industry in particular are unlikely to suddenly switch everything to Atom for a small increase in battery life because it would be very expensive and risky.

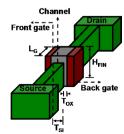

### Why FinFETs?

Feature size 22nm 7nm Bulk CMOS Gap Non-Si nano devices • FinFETs expected to continue transistor scaling to 7nm

- FinFET fabrication compatible with CMOS process

- FinFETs address scaling challenges faced by bulk CMOS

- Better channel control with double gates → reduced shortchannel effects

- Improved subthreshold slope

- Better Ion/Ioff

- Different styles

- Shorted-gate (SG)

- Independent-gate (IG)

- Asymmetric-workfunction SG (ASG)

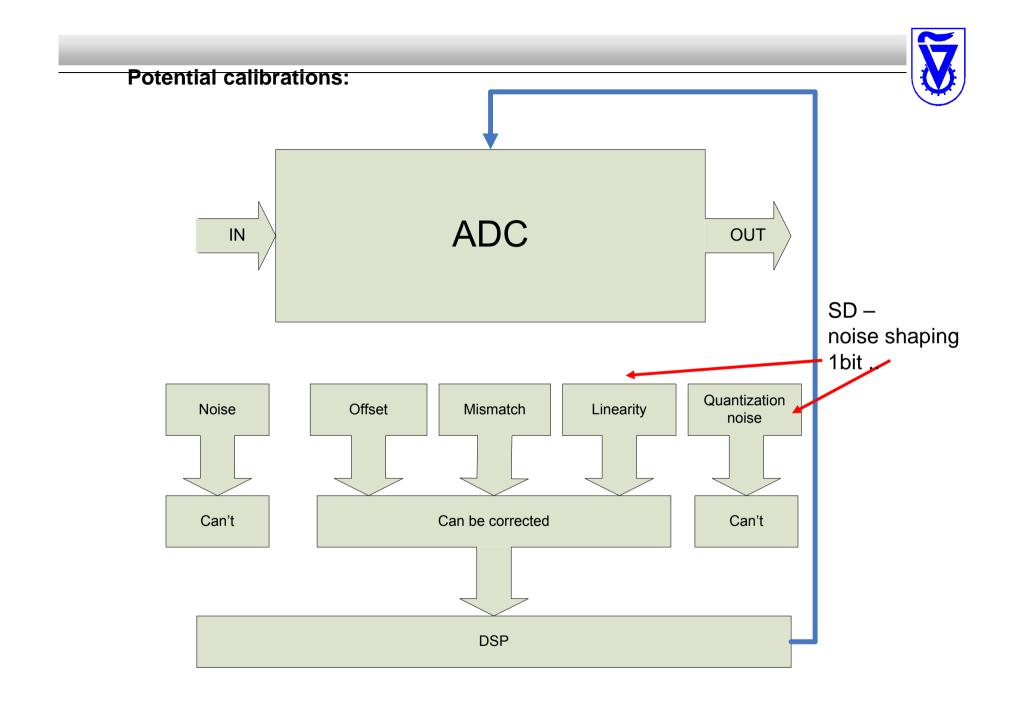

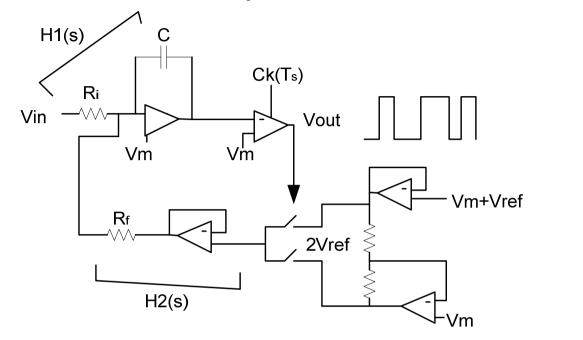

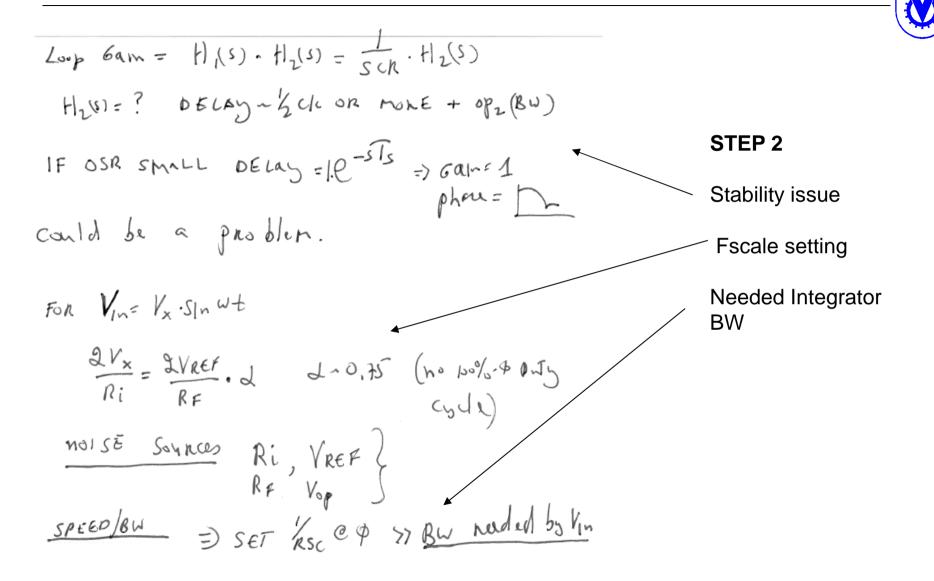

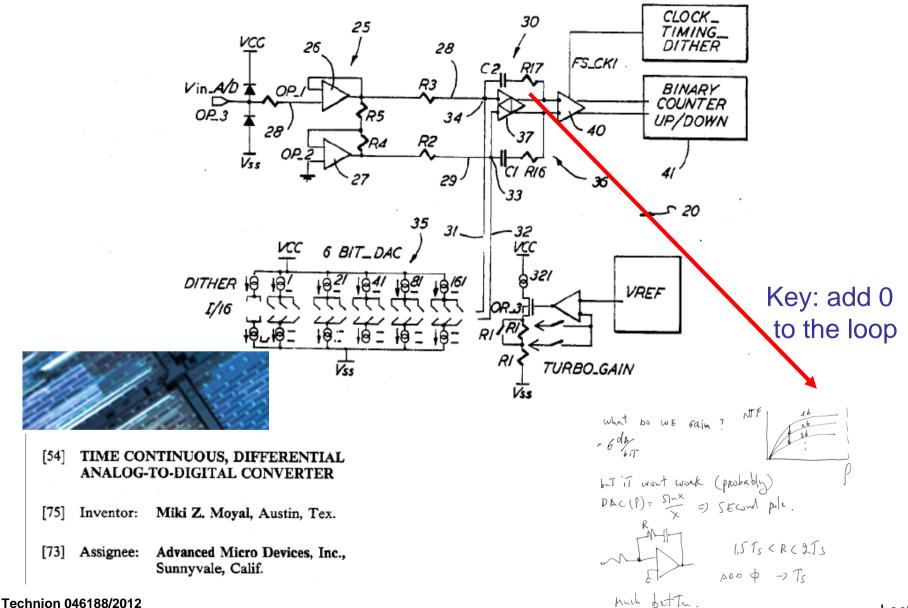

CT Sigma DELTA 1st Order Loop as an example

Objective : To be aware of the many issues of CT design

#### **Development of SD ADC**

Design "spec" For 84dB SNR

For input pk signal 500 mV

For BW=8 KHz

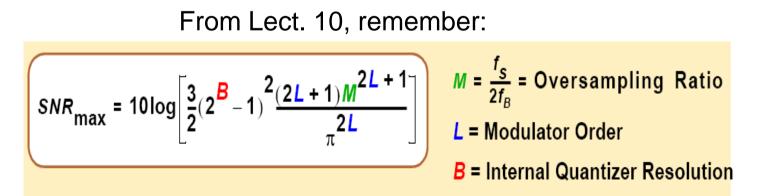

STEP 1 : SNR: Setting Clock Speed: (OSR) and inventory:

Let choose: One loop – Perfect linearity 1 bit DAC Vref/Rf 1 Comparator 200ua – 3ma (very fast) 1 Integrator 100uA – 2ma (very fast) References and clock signals 500uA Needed: DSP (Decimation filters)

#### SNR:

87db-6db(1bit) /9db/oct=9 octaves !

### Clock: 16KHz x 512 = 8.192MHz

STEP 3 : Noise sources findingRin and CFor 84dB SNR ( qunatization + Thermal Noises )linearities=0)For input pk signal 500 mVFor BW=8 KHz – phone: codec voice applications..

Input resistor should be as low as possible but also as large as possible (lower I dac, Low C, )

The maximum resistor is set by: Calculation of thermal noise to achieve 12dB higher SNR (96dB) (i.e., 10db added to 84dB will drop total SNR by ~ 1dB to 83dB)

#### Calculate Noise due to Rf and Ri

#### **STEP 3**

For signal input of 400mV: 96dB down from (1:65,536) = 6.1035uV (in 8 KHz) Find R and C Per sqrtHz=> 6.1035/89.44 ~ 68 nV For each of the 2 resistors: /1.414 (Rdac=Rin) = 48 nV/sqrtHz (room T) If 1K has 4.09nV/sqrtHz

**<u>R= 137 K ohm</u>** (will produce ~48nV/sqrtHz : 4.09 xsqrt(137)) I dac =  $0.5/137000 \sim 3.6$ uA (forgot to take temp in 4kT..)

#### Finding C:

For 8 KHz setting the op BW it ~2.5 time 8 KHz = need 68pF !

Lect 11

Note: Beyond this lecture but. Remember..

ADD made of 1 loop can be sensitive to "tone spikes" ( dithering is needed)- it take long fix sequence.. ( nice feature: SD "like" noisy environment..)

Slew rate and amplifier performance should be evaluated

Feedback C (add R to compensate for loop DAC ~integrator And simulate best values).

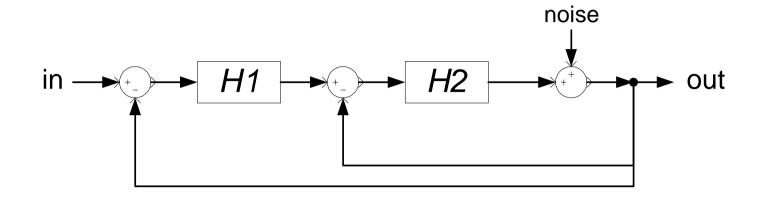

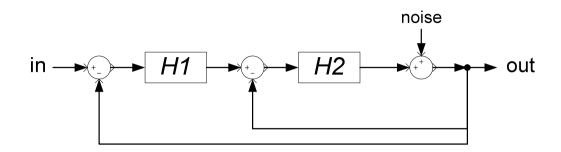

2 loops: Were to open the loop?

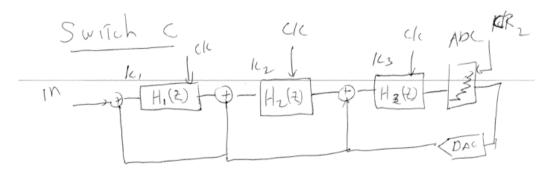

$$(noise = 0): \quad \frac{out}{in} = \frac{H_1H_2}{1 + H_2 + H_1H_2}$$

$$(in = 0): \quad \frac{out}{noise} = \frac{1}{1 + H_2 + H_1H_2}$$

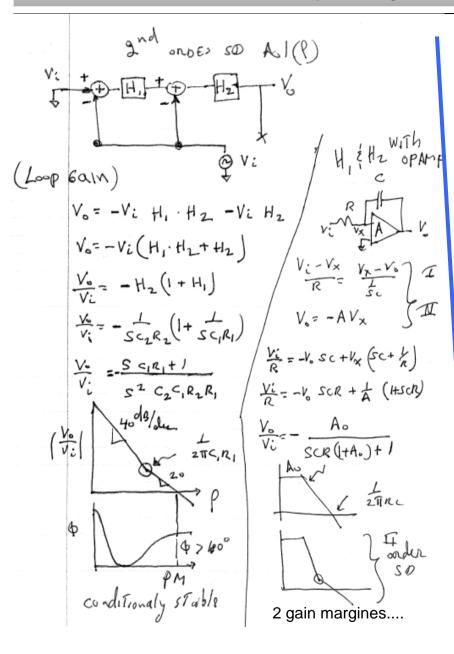

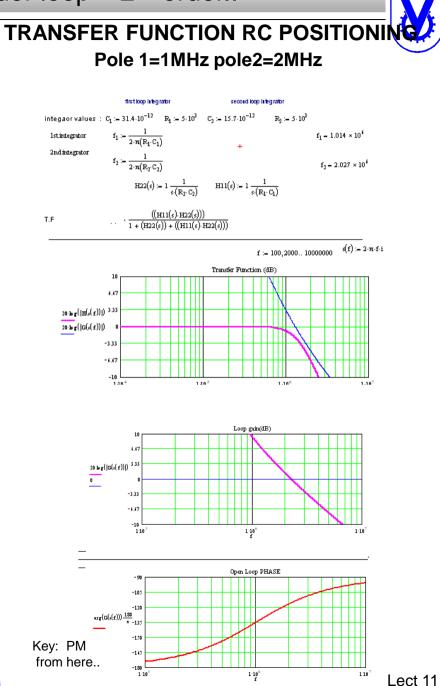

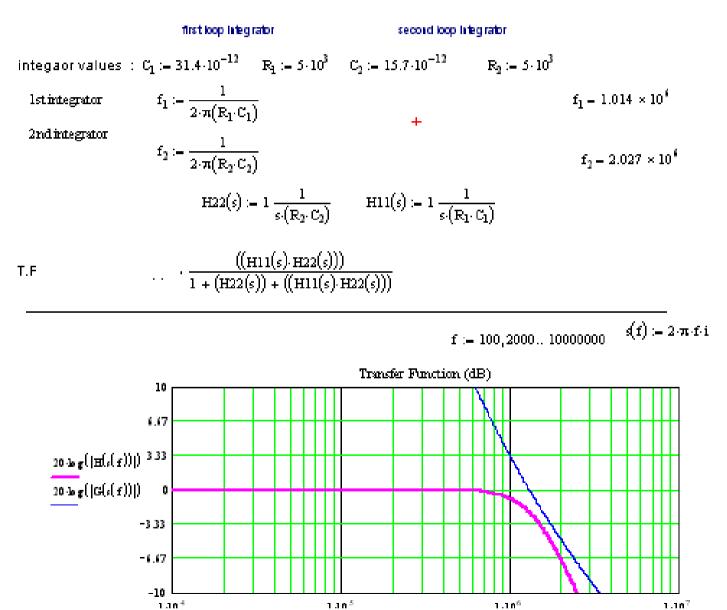

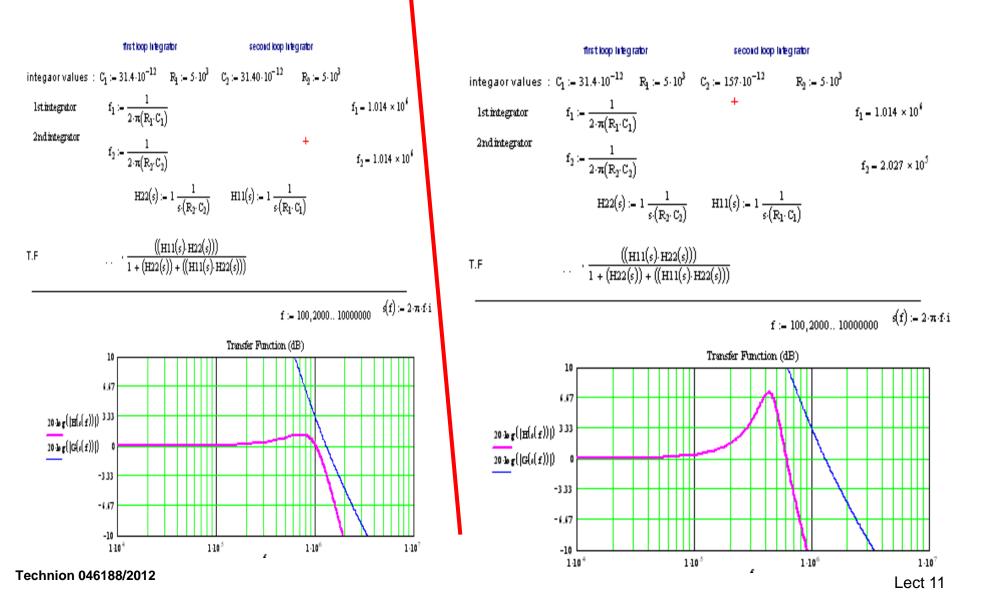

### Stability of higher order loop – 2<sup>nd</sup> order..

Technion 046188/201:

Lect 11

### Example: Stability "Wrong positioning"

Pole1~ 1MHz

Pole2~ 0.2MHz

#### Pole1~ 1MHz Pole2~1MHz

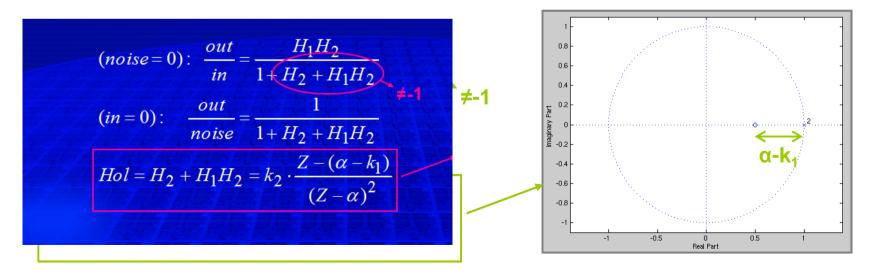

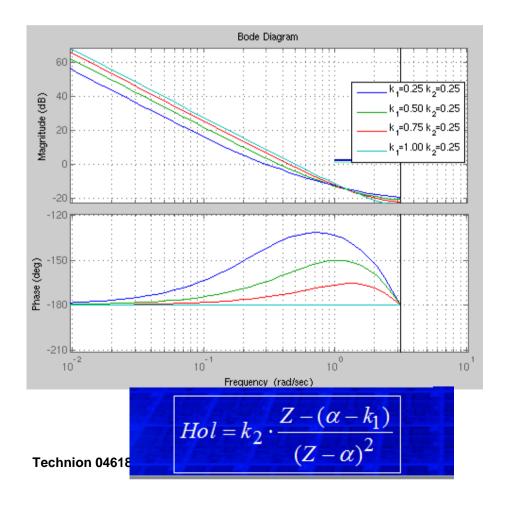

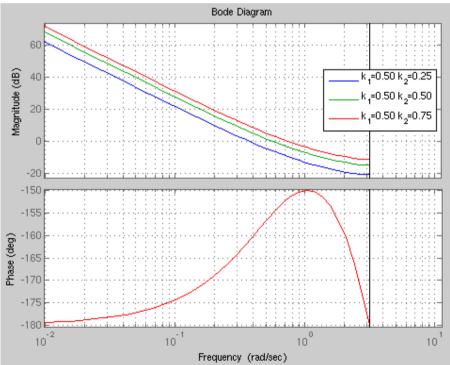

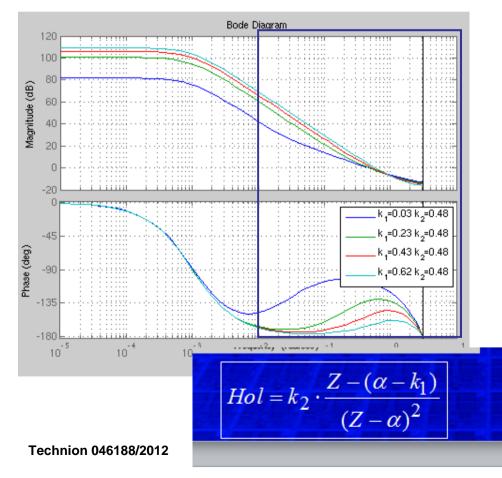

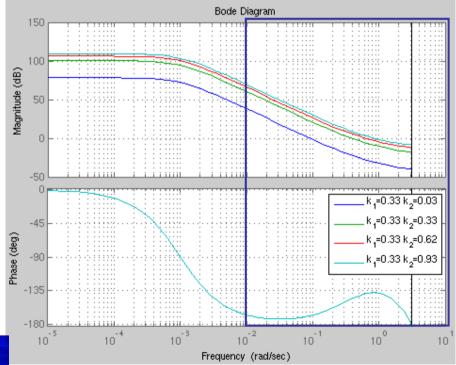

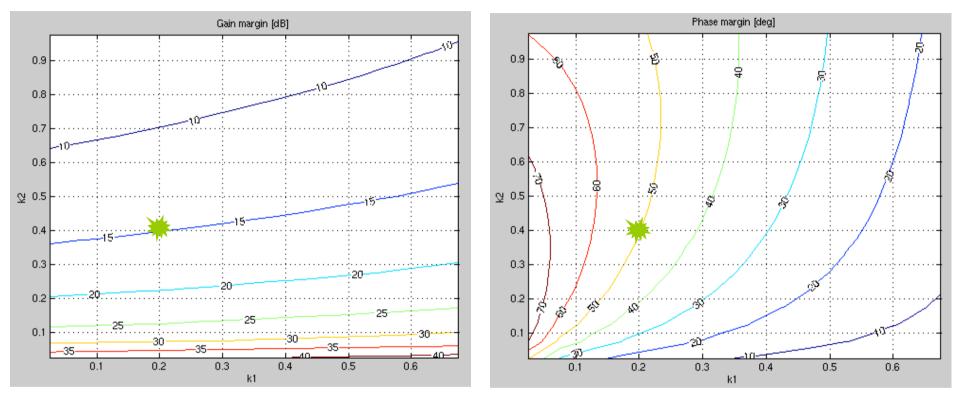

### Example: Stability noe in z domain..

- Each H is an integrator with delay:

- In Ideal Integrator α=1

- Transfer functions are:

- Constant k<sub>2</sub> varying k<sub>1</sub>

- Smaller k<sub>1</sub> increases phase margin noticeably

- Constant k<sub>1</sub> varying k<sub>2</sub>

- The phase is constant

- Higher k<sub>2</sub> increases phase margin noticeably

- Constant k<sub>2</sub> varying k<sub>1</sub>

- Smaller k<sub>1</sub> increases phase margin noticeably

- Constant k<sub>1</sub> varying k<sub>2</sub>

- The phase is constant

- Higher k<sub>2</sub> increases phase margin noticeably

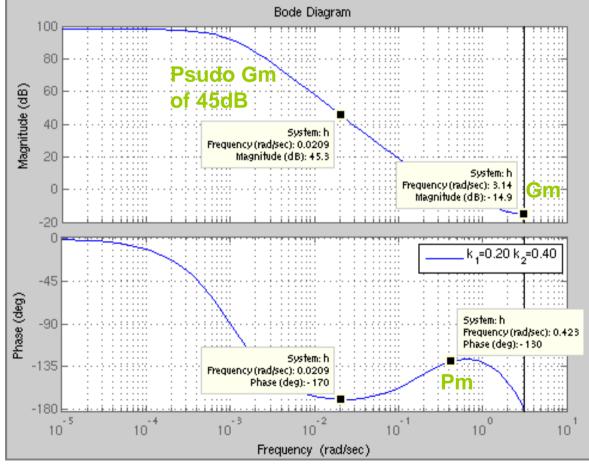

Stability Vs. k<sub>1</sub>,k<sub>2</sub>

- α has neglectable affect on the Gain-margin and Phasemargin

- The gain margin is always the gain at Fs/2

- i.e. k<sub>1</sub>=1/5 k<sub>2</sub>=2/5 Gm=15dB Pm=50°

• k<sub>1</sub>=1/5 k<sub>2</sub>=2/5 Gm=15dB

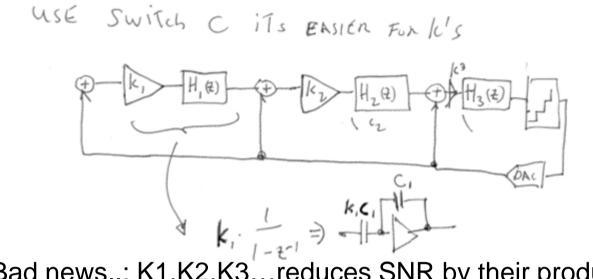

Stability: Introducing K1,K2,K3..Kn in the loop..

Bad news..: K1,K2,K3...reduces SNR by their product.. Good news system is stable.

Expand on lect. 10 to figure SNR:

$$SNR_{pl} = \left[ 2^{B} - 1 \right]^{Z} \cdot \left( 2n + 1 \right) \left( \frac{R}{\pi} \right)^{2n+1} \cdot Q_{0} \cdot Q_{1} \cdot Q_{2} \left( \frac{3\pi}{2} \right) \cdot V$$

B=number of bits, R =OSR, n=loops, a0=K1..

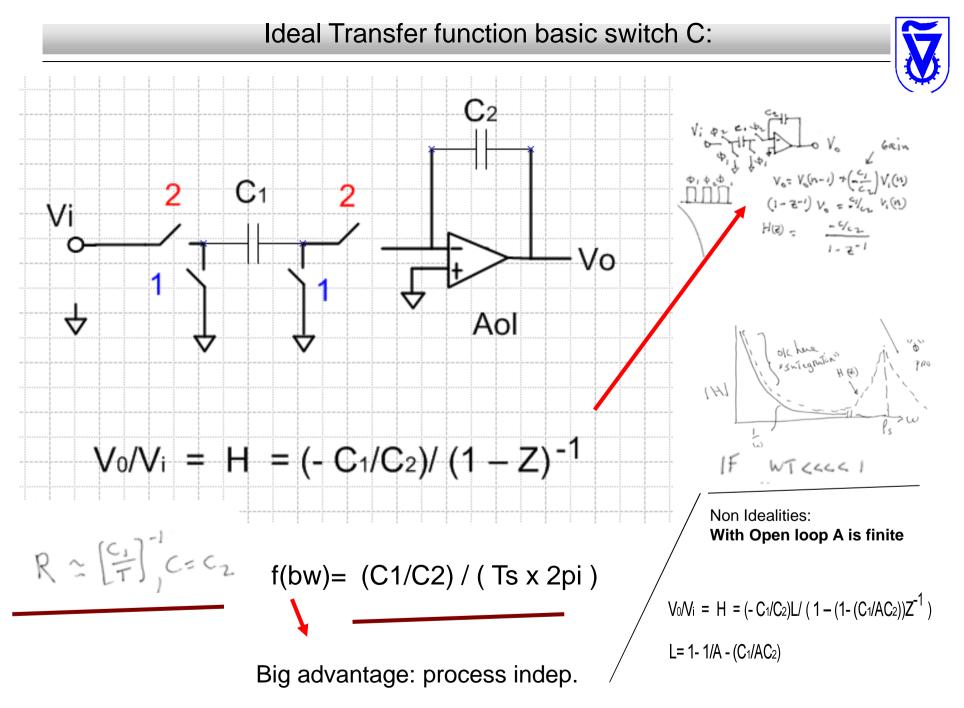

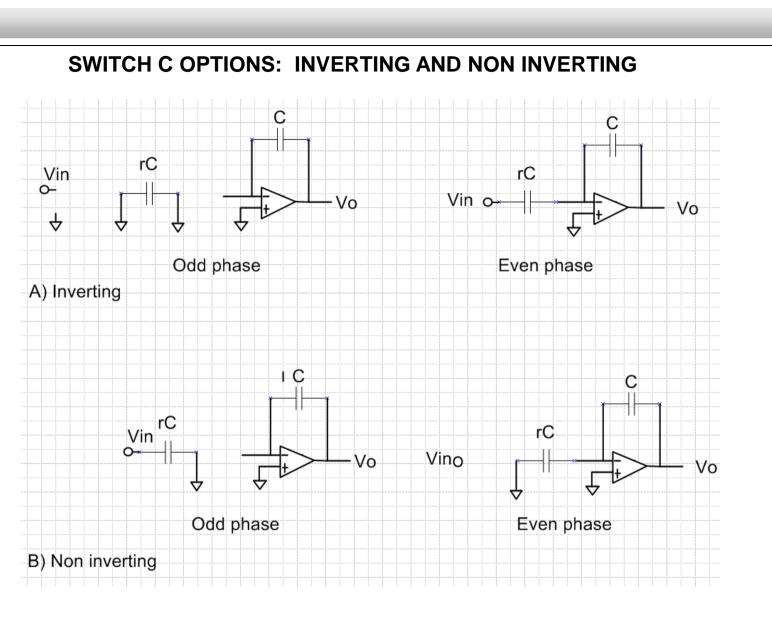

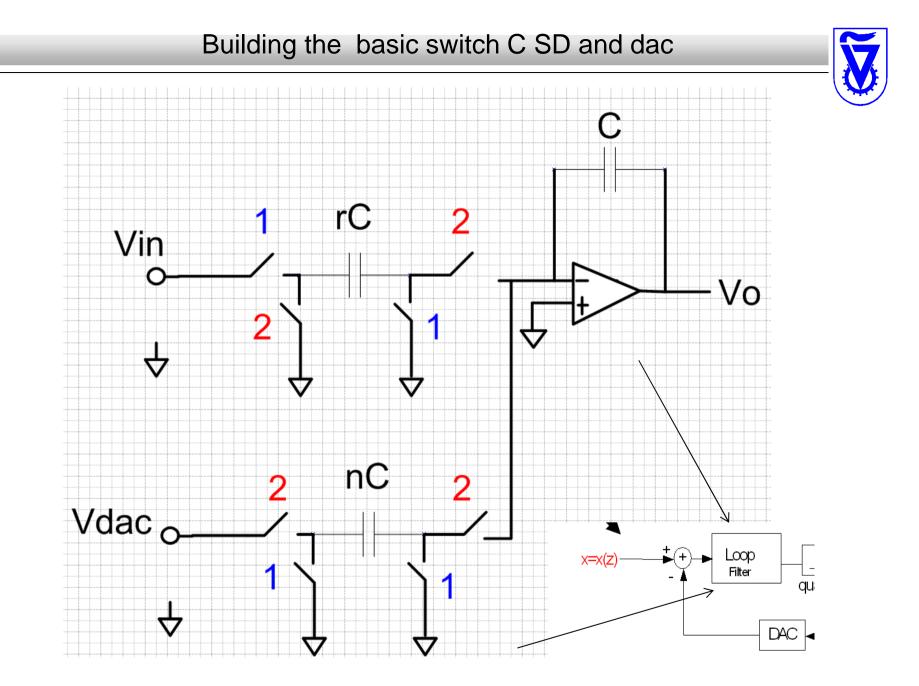

KEY: in SC WE CAN SUBSTRACT BY PLACING THE PHASE TIMING (no need for inverting amplifiers)

### EXAMPLE:

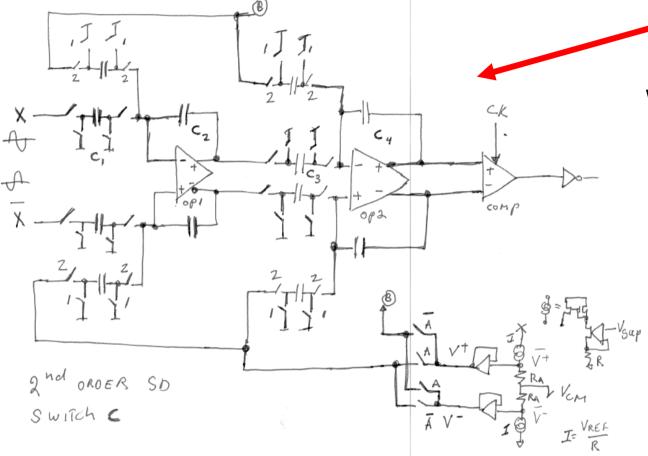

### Analysis of a Switch C Sigma Delta Second order

Analyze this second order SD How does it works? What is the potential SNR ?, Noise in ? max input signal BW ?

### Example: Given schematic and ckt parameters

What's going on ?

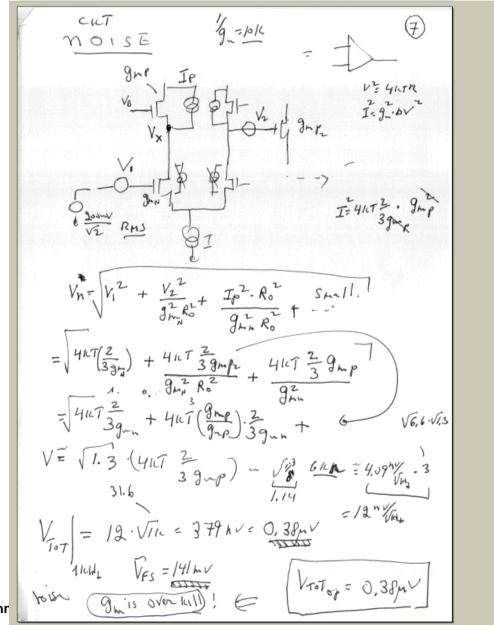

Given only : Clock rate => fck = 62 KHz , Vsigpk=0.2V C1 =100 ff , C3=100 ff C2= 1pf C4=0.5 pF op: gm=100e-6 1/ohm

Identify loop order Identify bit order Calculate integrator time constant values Calculate Ks – Stability issues Estimate max BW and potential maximum OSR Estimate effective number of bits, and SNR (quantization) Calculate noise sources (caps, Reference, devices)

#### **DESIGN** in class

(3)

$$R_1 = \frac{1}{c_1}$$

$f_1 = \frac{1}{c_1}$   $f_2 = \frac{1}{c_1}$

$B_{W} = \frac{1}{2\pi} \cdot \frac{c_1}{c_2}$

$R_1 = \frac{1}{2\pi} \cdot \frac{c_1}{c_2}$

$R_2 = \frac{1}{c_1} \cdot \frac{1}{c_2}$

$R_2 = \frac{1}{c_1} \cdot \frac{1}{c_2}$

$B_{W_1} = \frac{1}{c_1} \cdot \frac{1}{c_2}$

$B_{W_1} = \frac{1}{c_1} \cdot \frac{1}{c_2}$

$B_{W_1} = \frac{1}{c_1} \cdot \frac{1}{c_2}$

$B_{W_2} = \frac{1}{c_2} \cdot \frac{1}{c_2}$

590 25h= <u>64</u> 2×11= 3218 25 - 5 sogaves IF = GO Vph. SNm 5.g => 200+V  $\frac{20}{3} \frac{1}{3} \frac{1$

Cap hoisE  $(\mathcal{A})$ 1pF -> 64mV ->VICT diff stage. C. = 200 ft= 4.23 Vn cup = 17.875 xV

Techr

Lect 11

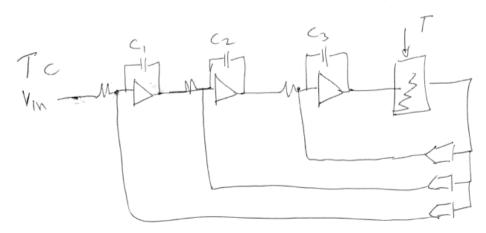

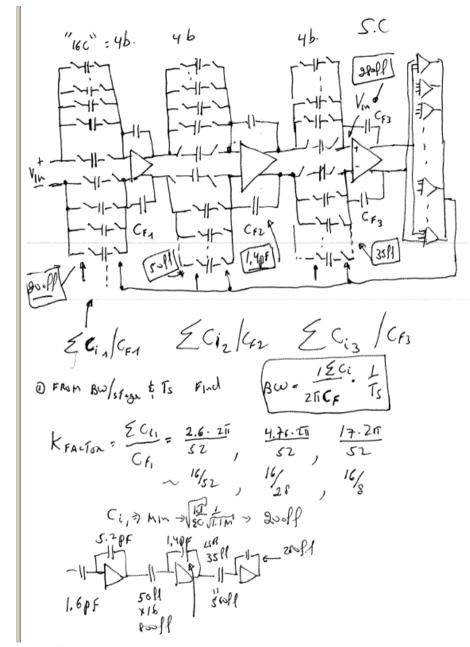

### **Design 3rd order Switch C and CT ADC**

D want Low/Lowest power  $(\overline{)}$ 2 want - 146 CONVERTER 840B PLASAR 3 Sigma pelta APC Given, Can't change A) TECHNOLOgy -> Let go with CHOS 0.35M, 3.3V B) Input Full schale -> VFS = 0.5V c) CLOCK - Can decide but 20-60 MHz

is TRIKEY LIMIT Show Don't want op need To Don't want charge ap in To USE CLOCK SPEED is TRIKEY EAST HEED OSR LARGE PLL Tomake FASTON LET'S GO WITH ~ MAX 52.8 MHZ \* SWR, LOOP, - SET IT but DEM! DOES >16! CecT~10-11

Want signal=1.1MHz ! Want 84dB (ADSL)

Design in both: TC and SC. Because some parameters are easier to calculate in TC some in SC

Vn

$$+ L_{avgs}$$

$+ L_{avgs}$   $+ L_{avgs}$

CONSTRUCTION of 84 dB LOW POWER. SD 2.2 Mb/s (1,1 MHz) EXAMPLE

NEXT CALCULATE K, K2, K3 5 USE Switch C its EASIER FOR K'S H, Q) 5 4 DAC k,C, 1st integration & crossing is the CLOSEST POLE of THET.F >, 1.1MHZ OR WE Won't PASS Signals. I TAKE 2.5 MH<sub>Z</sub> (Twice,) Too FAR AM ALLAND SANDAR WILL FORCE Foo CLUSE is ATTENNATION OTHER IC'S É MORE IMPONTANT O CLIPPING TO 60 4P.

$P_1 = \frac{1}{2 \operatorname{Tr}'' R'' C} = \frac{1 \cdot C_i}{2 \operatorname{Tr} C_F} T_s$ (6)  $P_1 = \frac{k_1 k_2}{2\pi k_1} l_s \qquad l_s = 52.8 \text{ MH}_2 \quad l_s = 2.5 \text{ MH}_2$  $K_1 = \frac{2.5}{59.8} \cdot 2\pi = 0.3$ 12=> should be ~ 2.5 f. f =) should be ~ 2.5 f =)  $l_1 = 2.5 h H_7 \rightarrow k_1 = 0.3 l$ P. = 6.25 MHZ - K2 = 0.75 Y 2 = 15.625 MH\_ -> K3 = 1.875 ) , STability qualysis, with mamber of bits (4) I) hoise TF can optimize The Value + 20% of the Raye! IN CT / Bu & Last op herd To be Large.

$\begin{aligned} \text{CAL CUL ATE SHR} \qquad & (i) \\ & \mathcal{B} = PAC \ biJs = 4 & Q_0 = k_1 = 0.3 \\ & Q_1 = k_2 & 0.875 \\ & R = 0SR & = 9.4 & Q_2 = k_3 & 1.845 \\ & NADC ONDER = 3 \\ & OVERIOND \ V = 0.75 \\ & OVERIOND \ V =$

Not bad we want 84 so we have some margin !

TC-3Nd, Buds, HMHA 1 CILI AOC TC (z STRUCTURES RL Pin l= 2πR,C; 1.1MHZ (max) CKZ 41 DAC (9.3 MAX BW) 567 The Integration Value's  $\begin{bmatrix} R_1 C_1 \Rightarrow 2 \cdot 6 & M H_2 &= \frac{1}{2\pi} \frac{1}{2} \cdot \frac{1}{10} \cdot \frac{1}{10} = 67 \text{ ms} \\ R_2 C_2 \neq 34.76 & M H_2 &= 36.87 \text{ ms} \\ R_3 C_3 \neq 3 & M H_M H_2 &= 10,32 \text{ ms} \end{bmatrix}$ 1st ints? 15 2.1 SETTIJ "FACTORS DRE  $R_1 C_1 = 67 ns$  $R_2 C_2 = 37 ns$ 1.83 ~2.36° 3.57 £ (1.1 MH2) R3c3=lons above 1.1 (AN) V2 29 NV/VUZ - D 25 M 0.57 >1964B VI.1.A MAXOR, = SET THE HOISE Vin osfacitant 100; ~ but controled 2-4- #PF MIN C3 = AS SMILL AS possible 5.61. 3.3K IFS= 80MA 6.6K IFS=== 10mA Irs=80MA 15 16 10 IF5" JLOB = SMA 2 6 IFS 5 -14-1-15-2

V

# End Lecture 11

www.gigalogchip.com