Welcome to 046188 Winter semester 2012 <u>Mixed Signal Electronic Circuits</u> Instructor: Dr. M. Moyal

Lecture 10

**Over Sampling ADCs : Sigma Delta - Loops and Architectures**

**SNR CALCULATIONS**

www.gigalogchip.com

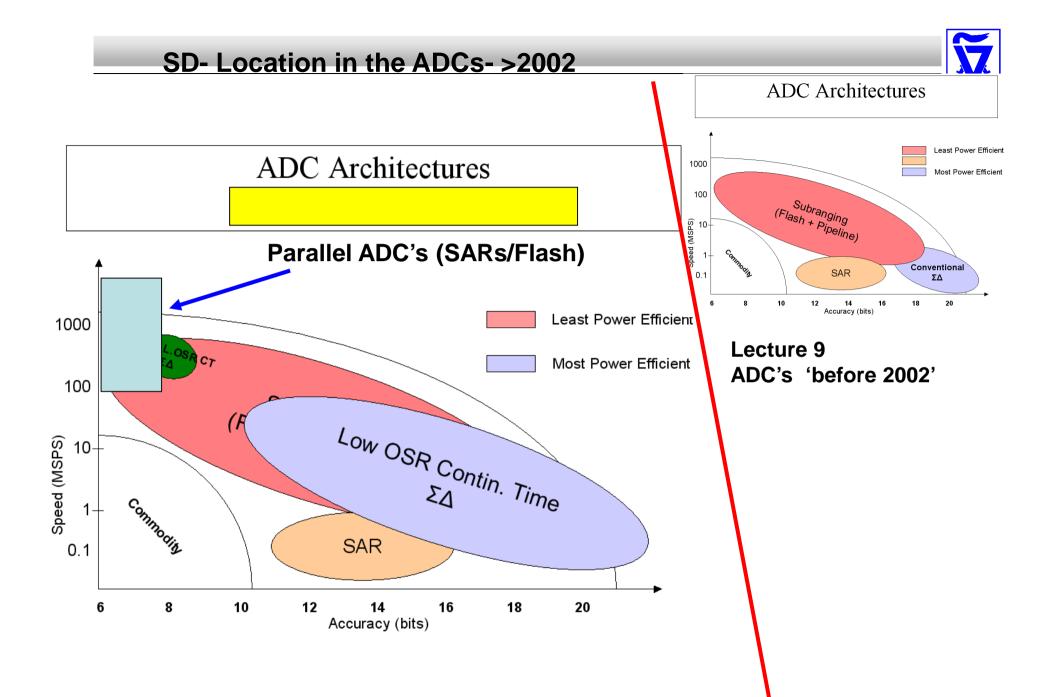

Sigma Delta – System Non Nyquist Converters

Why Over sample

Basic Loops, Z transform

Noise Transfer

Multi-Loops

Multi Bit Multi Loops

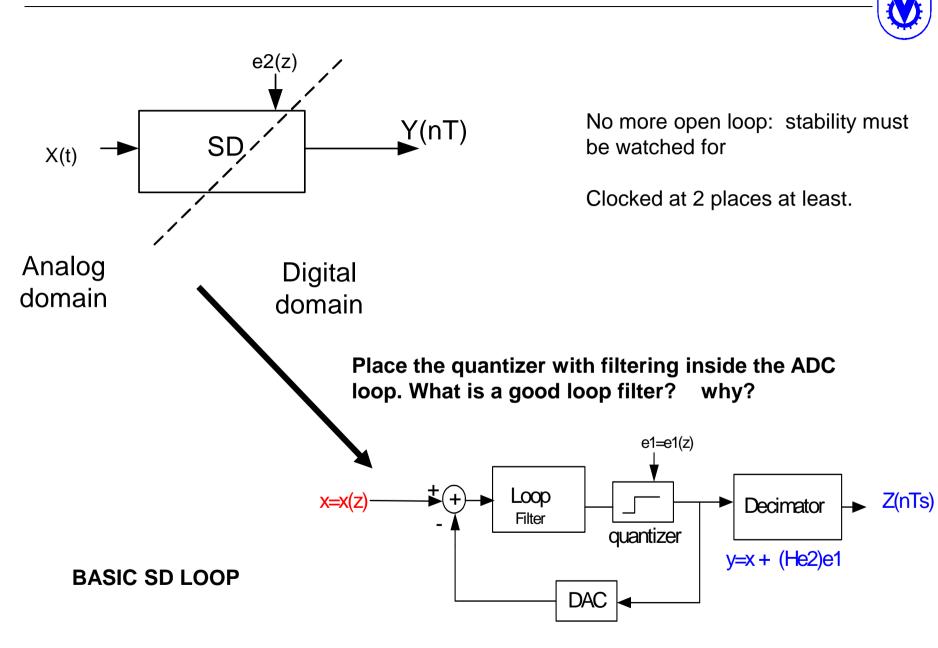

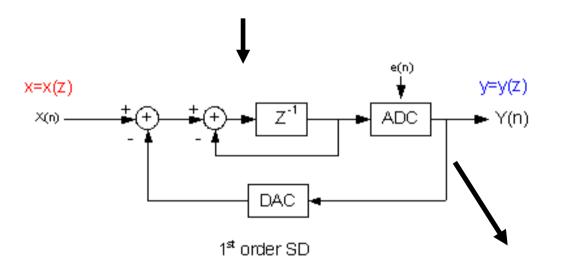

## **BASIC SD LOOP**

# MAIN OLD RESON LINEARITY IS INFINITE!

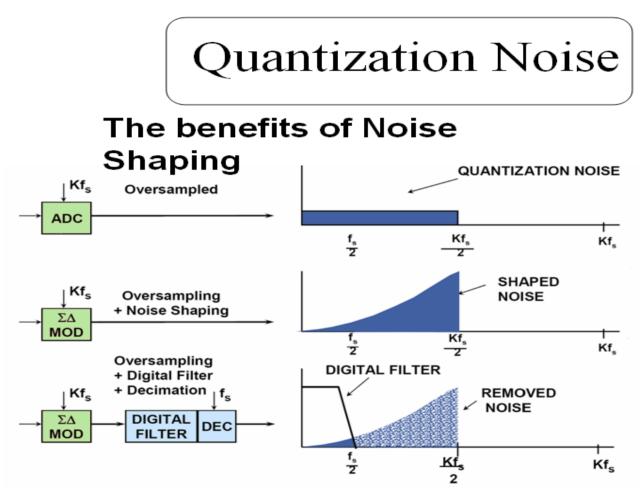

# Quantization Noise

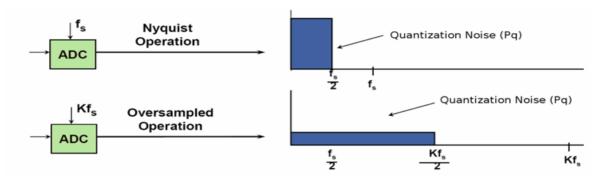

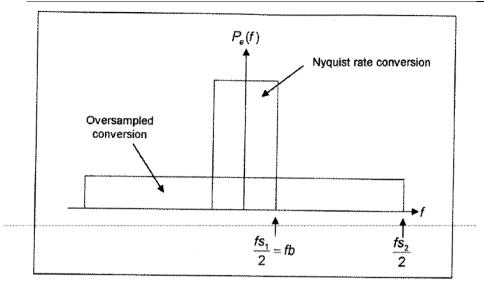

#### Nyquist vs Over-sampling Operation

$\Sigma$ -Delta architectures use oversampling; Normally, pipeline architectures do not

TRAIDING DIGITIZING RATE FOR BITS TO GET EQUAL QUANTIZATION NOISE IN A FIXED BAND

SNR INCREASE ===> f ( 10 log fs1/fs2)  $2x \rightarrow 10\log 2= 3dB$

When the noise is shaped equally (quantization noise) 2 x fs – Half noise power increase in SNR by 3dB 4 x fs - same as 1 bit performance increase N x fs – 10log(n) increase in performance

#### Example:

Use 8 bit converter over sample by 16 get 10 bit SNR

But is it the best we can do?

Poor return on investment (clock frequency increased - if noise spread equally

## Can we shape the noise in band ?

#### Can we shape the noise ?

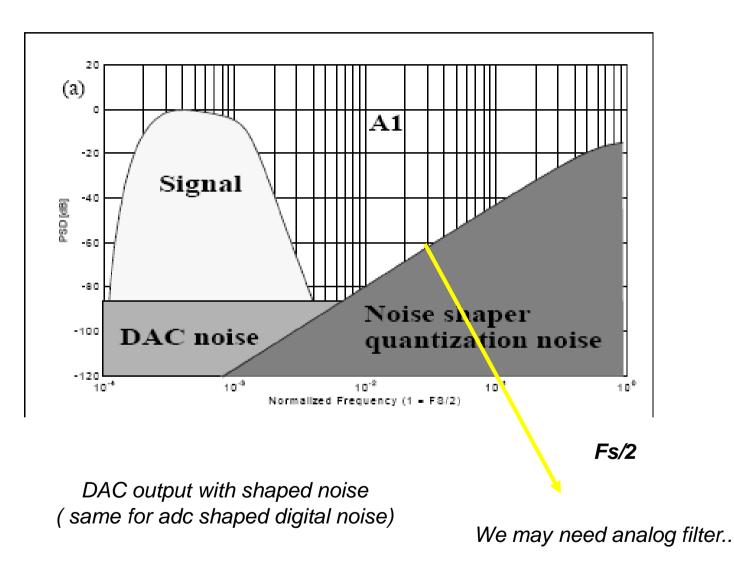

NOISE SHAPING Shape the quantization noise differently

We will need digital filter ..

## <u>Additional why's...</u> <u>Sigma Delta Converter "love digital noise"..</u>

Anti-alias filter relaxed No S/H- Reduced analog block requirements Easy re design for new technology, Low Voltage design Low power- Good FOM Fewer DAC bits

But, the minuses are: a feed back path, amplifiers.. and over sampling needed..

Nice: DONT FORGET WE CAN GET INFINITE LINEARITY ! But... Need much faster sampling clock

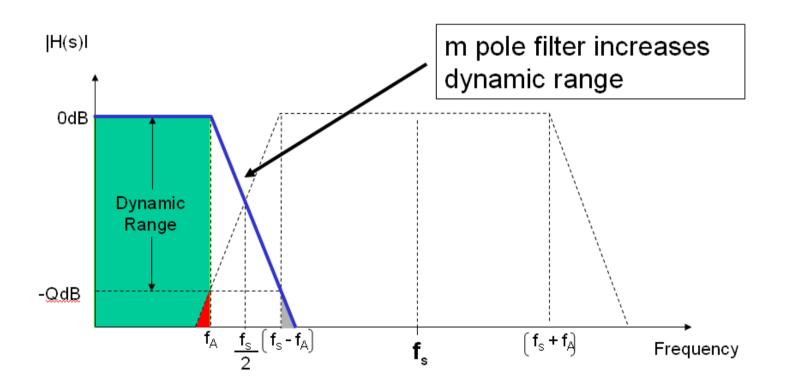

# **Relaxed Input Filter**

#### **Basic Loop- how does it work**

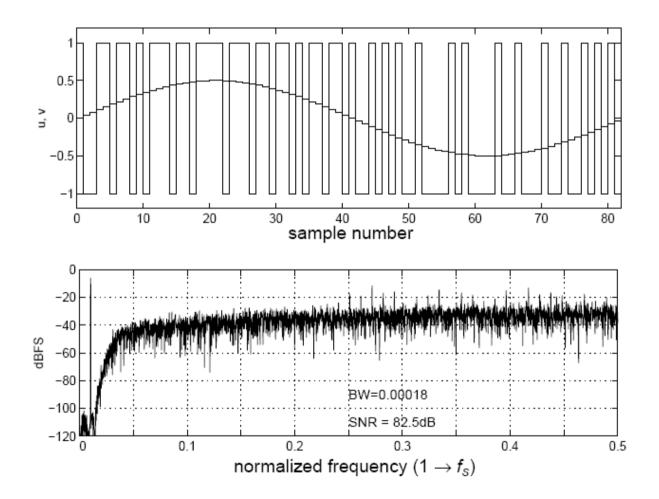

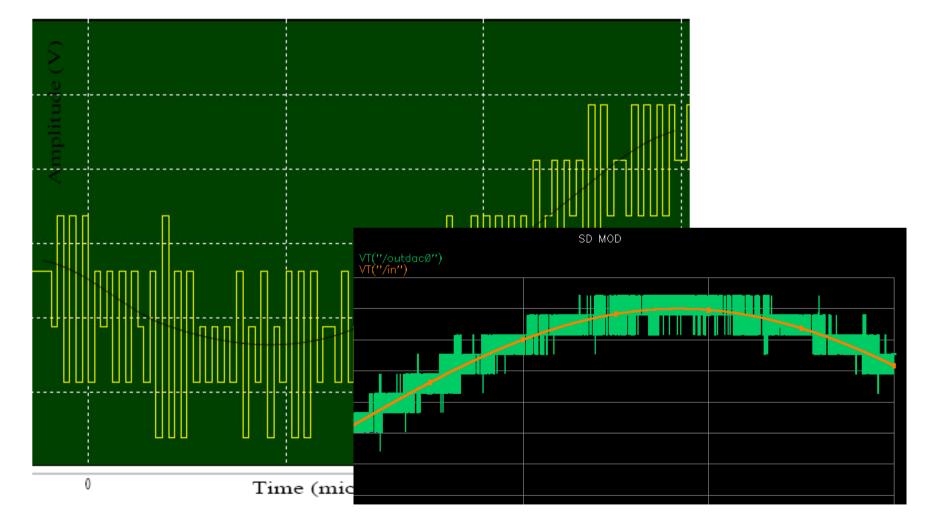

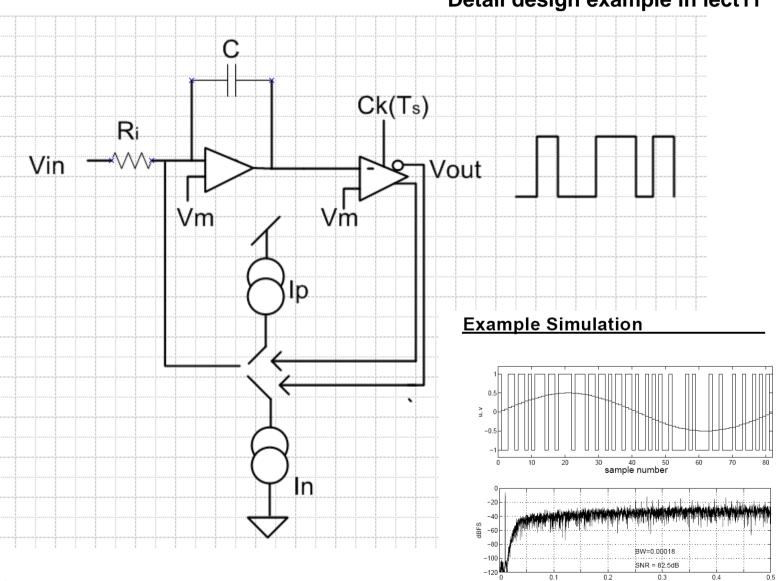

## **Example Simulation**

#### Example 2 - Multi bit SD- adc

Time domain multi bit over sample converter (converting digital bits to levels..)

NEXT :

Analyze SD structures, review few loops and...

#### HOW TO CALCULATE LOOP QUALITY: SNR

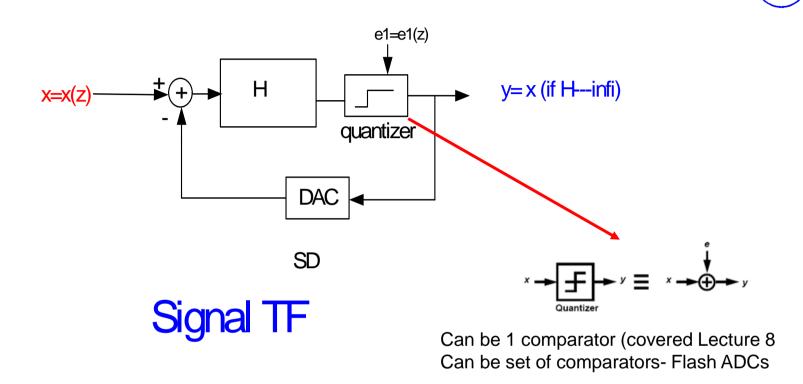

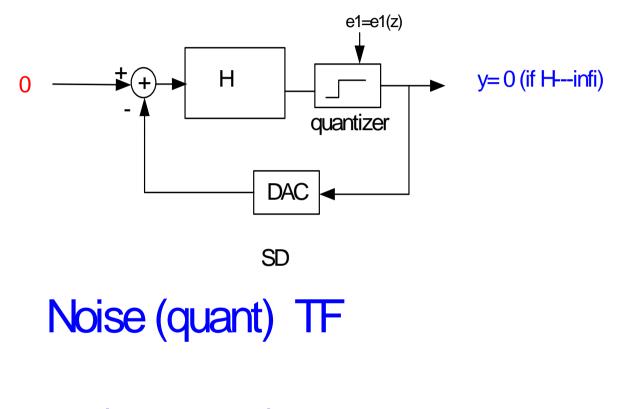

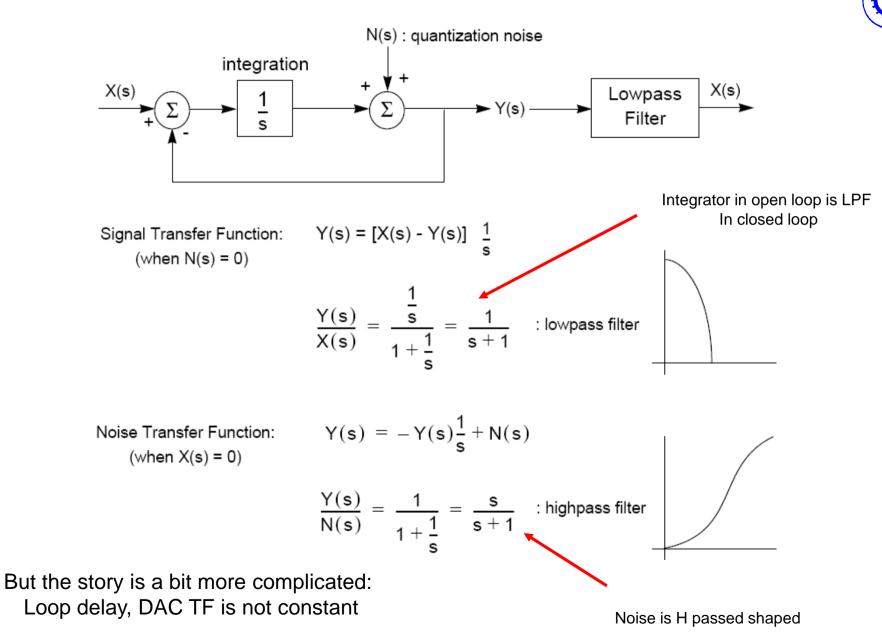

#### **Basic SD T. Function**

# Vout/Vin = H/1+H

if H (v. large) goes to infinite T.F = 1

Vout/Vin = 1/1 + H

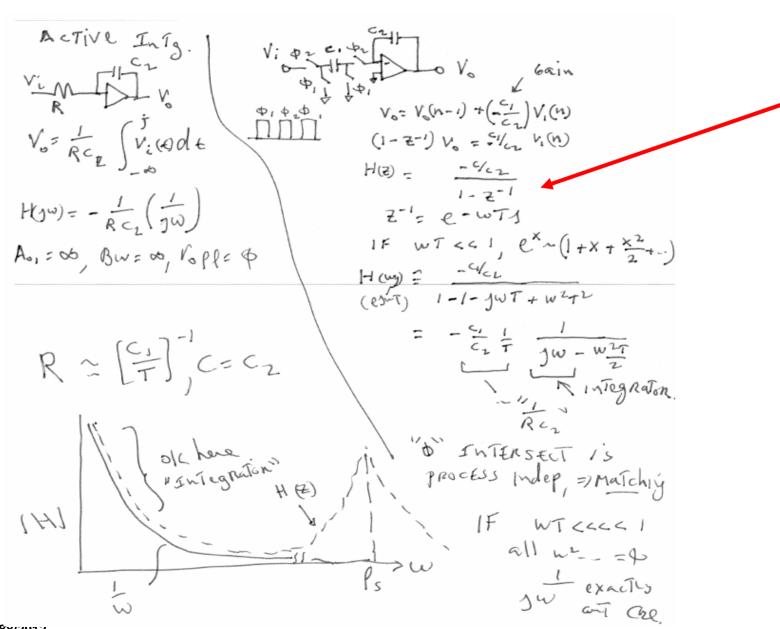

Let's assume its good to use an integrator in the loop

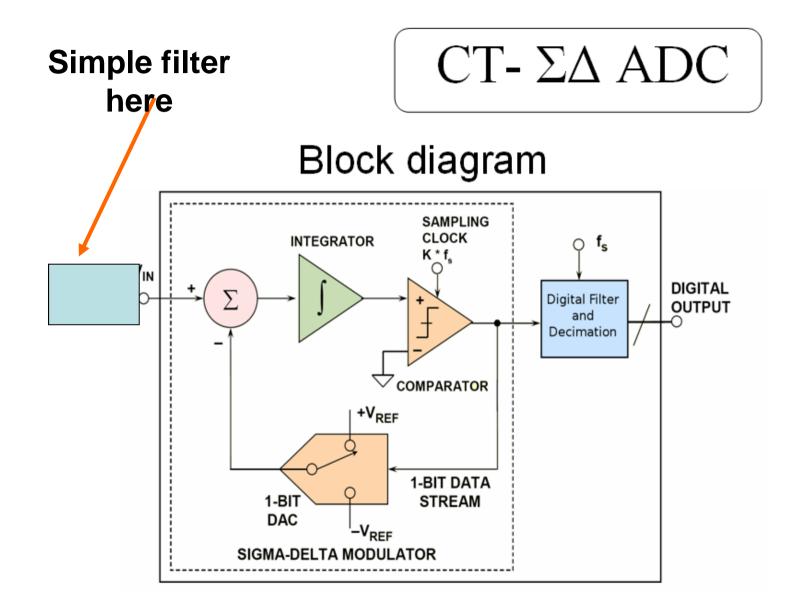

SD can be implemented using time continuous filters (integrators) but also using switch capacitor- discrete time..

To further study of SD I will switch back and force from time domain to Discrete domain- some calculations are easier to explain in one domain or the other.

# Look first at analog sigma delta simple 1 loop

## SD analog model for TF

#### **SD** continuous analog blocks

Detail design example in lect11

normalized frequency  $(1 \rightarrow f_s)$

## **SD** - Noise analysis Vs. loop order

SUMMARY

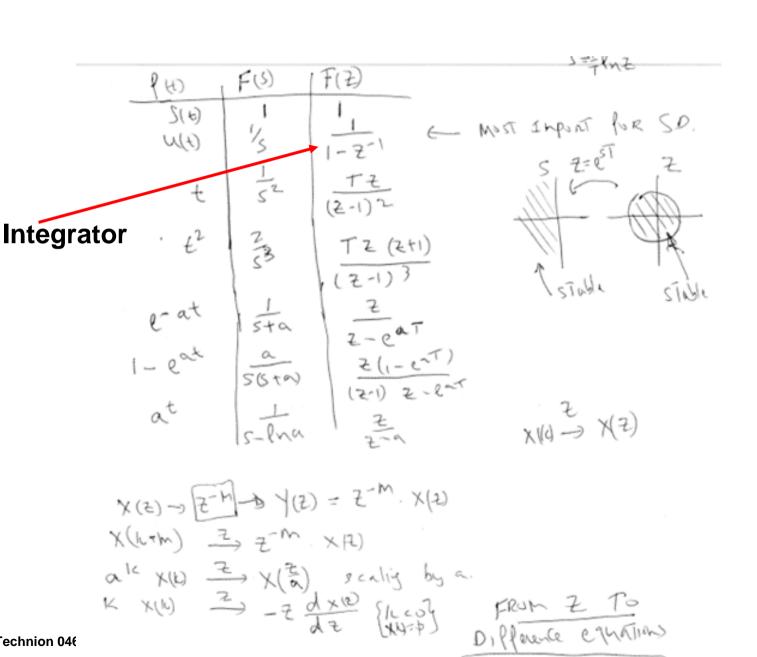

$$\rightarrow Z$$

TRANSFORMATION

1) TAILE P(H)  $\rightarrow Z$  TRANSFORMATION

1) TAILE P(H)  $\rightarrow Z$  P(H)  $\rightarrow Z$  S(H-1CT)

1) CREATE P\*(H)  $\rightarrow Z$  P(H)  $\rightarrow Z$  S(H-1CT)

1) TAILE Laplace TRANSFOR of P\*(H)  $\rightarrow F(S) = \sum_{l \in O} P(let) e^{-let}$

1) REPLACE S by  $\frac{1}{T} ln(z)$

1F  $Z \triangleq e^{TS} = e^{3wT} \Rightarrow F(z) = Z(P(H)) \stackrel{a}{=} \stackrel{a}{F}(z) = \sum_{l \in O} P(let) z^{-le}$

#### Transfer to distinct values- X(nT)

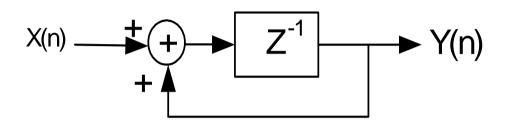

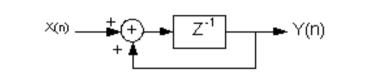

Differences eq. can be easily described: Y(n) = X(n-1) + Y(n-1)

Technion 046188/2012

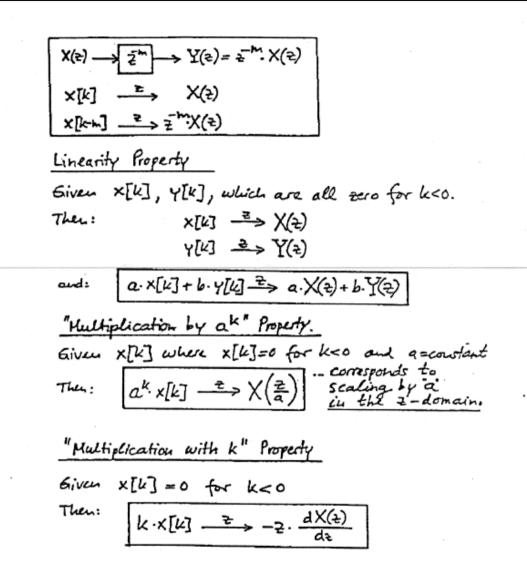

#### Quick look at Z domain

Technion 046

#### Z domain basics

From "z" to difference equations

## Z domain Integrator

Discrete time integrator

$H = Z^{-1} / 1 - Z^{-1}$

Differences eq: Y(n) = X(n-1) + Y(n-1)

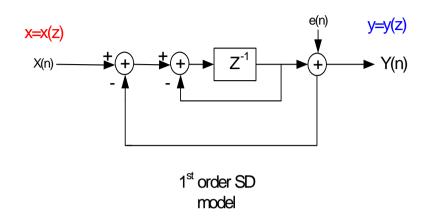

#### build the SD: lets put the integrator in the loop/s

$H = Z^{-1} / - 1 - Z^{-1}$

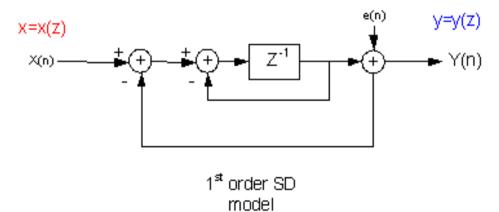

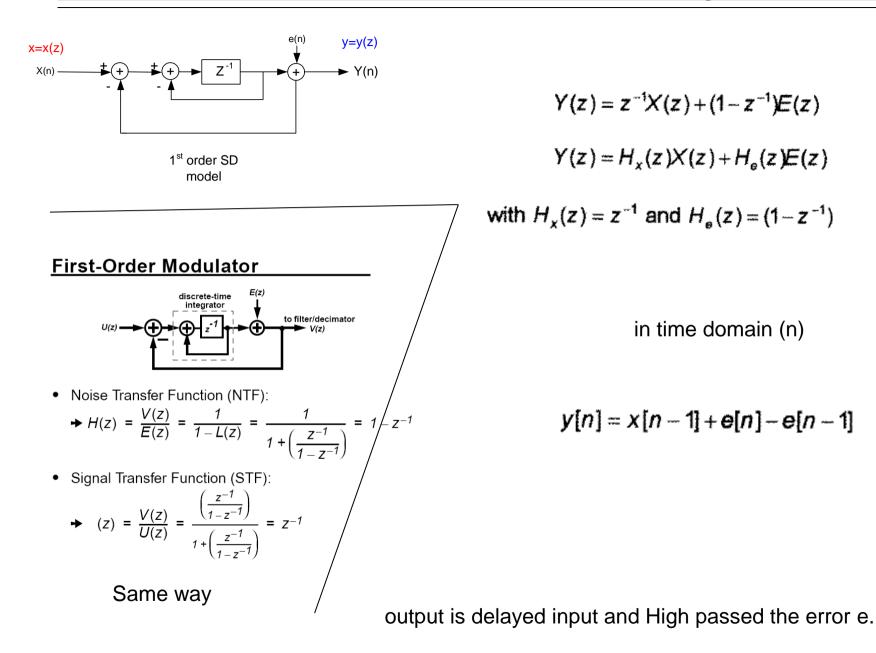

#### build the SD: TF calculations 1 Loop

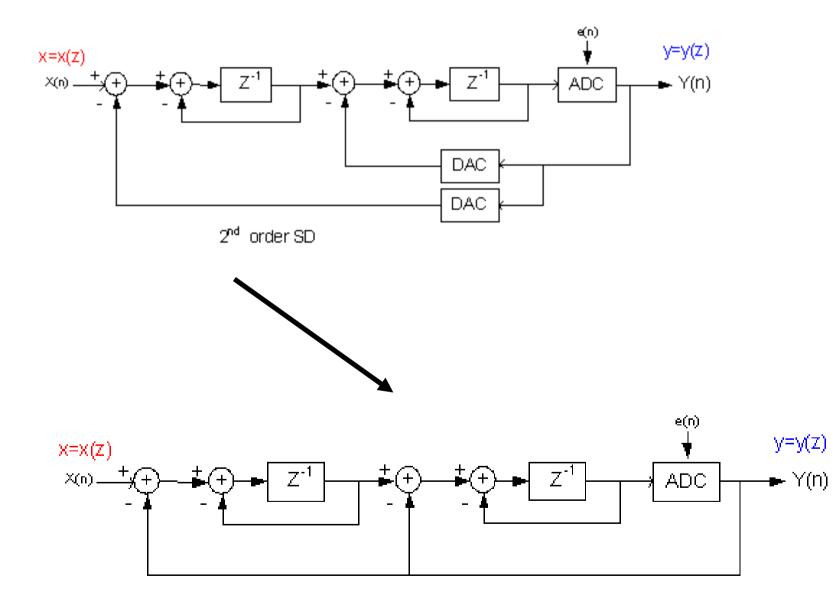

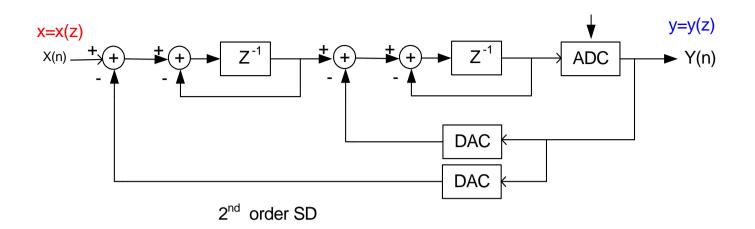

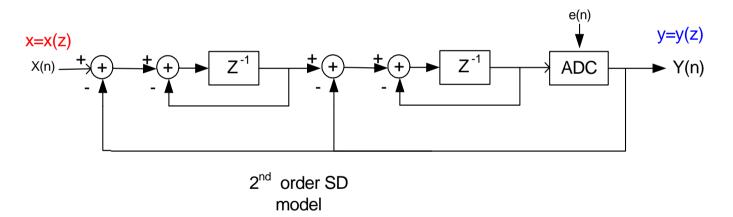

#### **Build the SD: 2 Loops**

SNR IMPROVMENTS AND TF CALCULATIONS

#### HOW TO CALCULATE LOOP SNR

Technion 046188/2012

#### **Uniform distribution of noise**

The noise density power spectra density is

$$\sigma_e^2 = \frac{\Delta^2}{12} = \frac{1}{12} \left(\frac{2V}{2^N - 1}\right)^2 \equiv \frac{1}{12} \left(\frac{2V}{2^N}\right)^2$$

$$SNR = 10\log\left(\frac{\sigma_x^2}{\sigma_e^2}\right)$$

$$N(f) = \frac{\Delta^2}{12} * \frac{1}{fs}$$

$$\sigma_{ey}^{2} = \int_{-fb}^{fb} P_{ey}(f) df = 2 \int_{0}^{fb} P_{ey}(f) df = \int_{0}^{fb} \frac{2\sigma_{e}^{2}}{fs} df = \sigma_{e}^{2} \left(\frac{2fb}{fs}\right)$$

$$M = \frac{fs}{2fb} \text{ is called the OverSampling Ratio (OSR)} \quad \blacktriangleleft$$

noise improvements: 3 dB/ octave

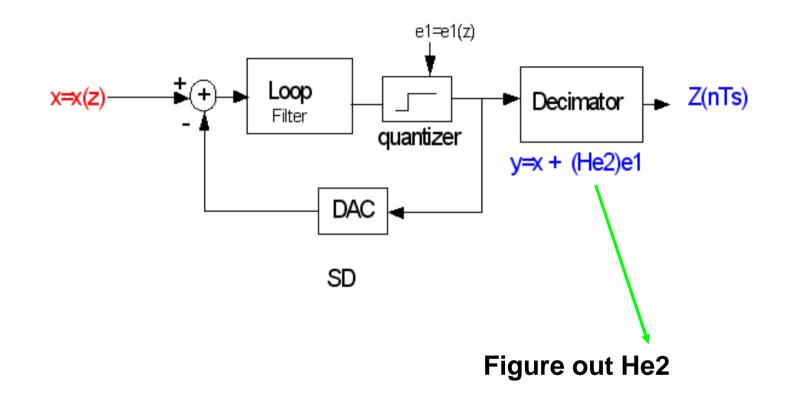

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z)$$

$$Y(z) = H_x(z)X(z) + H_e(z)E(z)$$

with  $H_x(z) = z^{-1}$  and  $H_e(z) = (1 - z^{-1})$

SNR calculations Z= exp (ST) Look only at the magnitude

$$\sigma_{ey}^{2} = \int_{-fb}^{fb} P_{ey}(f) df = 2 \int_{0}^{fb} P_{ey}(f) df = \int_{0}^{fb} P_{e}(f) |H_{e}(f)|^{2} df = \int_{0}^{fb} \frac{\sigma_{e}^{2}}{fs} |1 - e^{-j\omega t}|^{2} df$$

$$\sigma_{ey}^{2} = \sigma_{e}^{2} \frac{\pi^{2}}{3} \left(\frac{2fb}{fs}\right)^{3}$$

$$SNR = 10 \log(\sigma_x^2) - 10 \log(\sigma_e^2) - 10 \log(\frac{\pi^2}{3}) + 9.03r$$

~9db/ octave : doubling the sampling frequency reference to twice the maximum signal BW.

Remember DAC and ADC in the loop makes the delta LSB noise 6.02 x number of bits

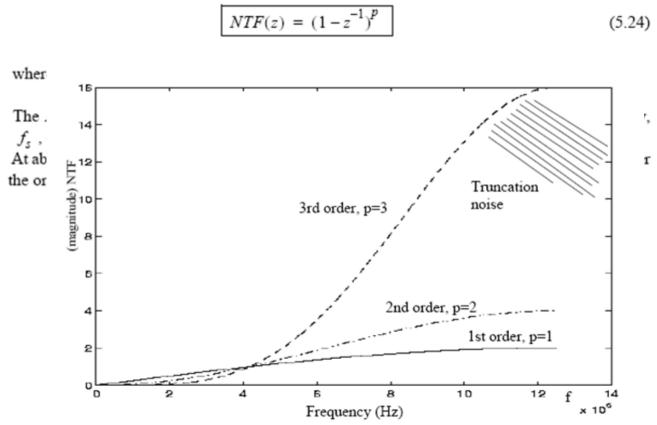

$$NTF(z) = 1 - z^{-1}$$

(5.17)

$$: \left| 1 - e^{-jwT_{s}} \right| = \sqrt{[1 - \cos(wT_{s}) + j\sin(wT_{s})][1 - \cos(wT_{s}) - j\sin wT_{s}]}$$

(5.18)

Combining the geometric terms of Eq. (5.18) yields,

$$|NTF(f)| = \sqrt{2 - 2\cos(2\pi fT_s)}$$

(5.19)

For a first order noise shaper, the noise power level improvement between any two frequencies, f and 2f is given by squaring and integrating Eq. (5.19) from f to 2f

$$\int_{f}^{2f} NTF(f) df = 2 - \frac{2\sin(2\pi T_s)}{2\pi T_s} = 8.8 \text{ dB/octave}$$

(5.20)

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})^{2}E(z)$$

$$Y(z) = H_{x}(z)X(z) + H_{e}(z)E(z)$$

with  $H_{x}(z) = z^{-1}$  and  $H_{e}(z) = (1 - z^{-1})^{2}$

Technion 046188/2012

$$y[n] = x[n-1] + e[n] - 2e[n-1] + e[n-2]$$

$$\sigma_{ey}^{2} = \int_{-fb}^{fb} P_{ey}(f) df = 2 \int_{0}^{fb} P_{ey}(f) df = \int_{0}^{fb} P_{e}(f) df = \int_{0}^{fb} P_{e}(f) |H_{e}(f)|^{2} df = \int_{0}^{fb} \frac{\sigma_{e}^{2}}{fs} |1 - 2e^{-j\omega\tau} + e^{-j2\omega\tau}|^{2} df$$

$$\sigma_{ey}^{2} = \sigma_{e}^{2} \frac{\pi^{4}}{5} \left(\frac{2fb}{fs}\right)^{5}$$

#### if r is the number of octaves

$$SNR = 10 \log(\sigma_x^2) - 10 \log(\sigma_e^2) - 10 \log(\frac{\pi^4}{5}) + 15.05r$$

Source : miki thesis

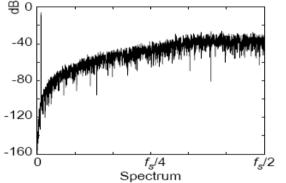

The advantage of the NS is that the noise is spread out to the higher frequencies to a location where the signal band is not used. The general form of the NTF(z) is given by

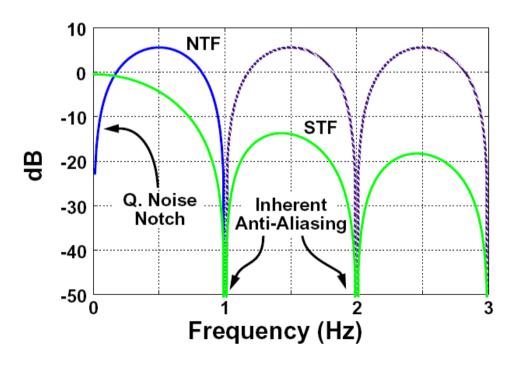

Figure 27: Simulation plot of NS truncated error coefficient

# **Modulator Performance**

- 1st-order modulator:

- 1st-order highpass NTF

- 9-dB SNR increase per octave OSR

- i.e. 1.5 bits/octave! (compared with 0.5-bit/octave for white noise)

- 2nd-order modulator:

- 2nd-order highpass NTF

- 15-dB SNR increase per octave OSR

- i.e. 2.5 bits/octave!

- *Nth-order modulator:*

- Nth-order highpass NTF

- 6N+3 dB SNR increase per octave OSR

- i.e. *N*+0.5 bits/octave!

#### **Multi-Loops- SNR Summary**

## **Frequency Responses**

#### What is really going on:

For 1st order the integrator become LPF and the 1-z-1 is 2-coswt to the N

#### **DESIGN EXAMPLE:**

(assume a's all 1)

Spec: VFs=1v, Design an ADC for : SNR>86dB, (>14b), fin=0-8KHz, Extra constrain: Power <2ma, Vdd=3.3v.

#### **Objective:**

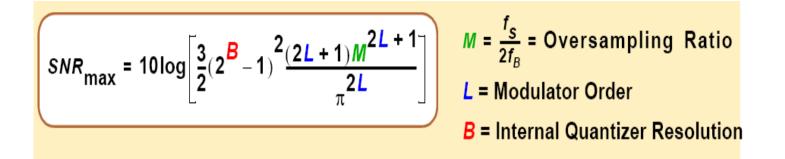

We need to determin: Loop Order , DAC number of bits, smf Fclock

| Option I                          | SigmaD ADC S                      | NR(quantization)                       | CALCULATIO                    | N                                | miki |

|-----------------------------------|-----------------------------------|----------------------------------------|-------------------------------|----------------------------------|------|

| DACS Nun<br><b>B</b> := 5.0       | nber of Bits []                   | Oversampling Ratio []<br>R := 128      | ADC Order []<br><b>n</b> := 1 | Overload Voltage []<br>V := 0.75 | _    |

| Integrator loop coefficients[]    |                                   | Fin maximum                            | Boltzman condt and Temp[]     |                                  |      |

| <b>a0</b> := 1.0 <b>a1</b> := 1.0 | 0 <b>a2</b> := 1.0 <b>a3</b> := 1 | $\textbf{Fin} \coloneqq 8 \times 10^3$ | ${f Kb}:=1.38	imes 10^{-23}$  | <b>Тетр</b> := 293               |      |

1. 1st-order SDM, 5-bit -Quantizer, fs=2.048 MHz, Fin=8 KHz

#### **SNR-** Equation

Maximum SNR

$$\mathbf{SNRpk} := \left[ (2)^{\mathbf{B}} - 1 \right]^2 \cdot (2\mathbf{n} + 1) \cdot \left( \frac{\mathbf{R}}{\mathbf{\pi}} \right)^{(2\mathbf{n}+1)} \cdot \mathbf{a0} \cdot \mathbf{a1} \cdot \mathbf{a2} \cdot \mathbf{a3} \cdot \left( \frac{3 \cdot \mathbf{\pi}}{2} \right) \cdot \mathbf{V}$$

$\mathbf{SNRpk} = 6.892 \times 10^8$

In dB

$\textbf{SNRdBpk} \coloneqq 10 \cdot \textbf{log}(\textbf{SNRpk})$

**SNRdBpk =** 88.383

Thermal Noise Requirements If we make the converter with switch cap then the noise...

$$\begin{aligned} \operatorname{Cin} &:= 1 \times 10^{-12} \\ & \mathbb{V}\operatorname{nqcap} := \left(\frac{\operatorname{Kb}}{\operatorname{Cin}}\right)^{0.5} \left[ \left(\frac{\operatorname{Temp}}{\operatorname{Fin}}\right)^{0.5} \right] \cdot \frac{1}{1} \\ & \mathbb{V}\operatorname{nqcap} = 7.109 \times 10^{-7} \\ & \mathbb{V}\operatorname{nqcap} := \left(\frac{\operatorname{Kb}}{\operatorname{Cin}}\right)^{0.5} \left[ \left(\frac{\operatorname{Temp}}{1}\right)^{0.5} \right] \cdot \frac{1}{1} \\ & \mathbb{V}\operatorname{nqcap} = 6.359 \times 10^{-5} \\ & \operatorname{SNRdBcap} := 20 \cdot \log \left(\frac{\mathbb{V}}{\mathbb{V}\operatorname{nqcap}}\right) \\ & \operatorname{Fck} := 2 \cdot \operatorname{R} \cdot \operatorname{Fin} \\ & \operatorname{Fck} = 2.048 \times 10^{6} \\ & \operatorname{SNRdBcap} := 20 \cdot \log \left[ \left(\frac{\mathbb{V}}{\mathbb{V}\operatorname{nqcap}}\right) \left[ \left(\frac{\operatorname{Fck}}{2.\operatorname{Fin}}\right)^{0.5} \right] \cdot \frac{1}{1} \right] \\ & \operatorname{SNRdBcap} = 102.506 \end{aligned}$$

The capacitance noise concern to 8 KHz so we get 102dB

Technion 046188/2012

| Option II SigmaD ADC SNI                                          | CALCULATION                        | miki                                |                                  |

|-------------------------------------------------------------------|------------------------------------|-------------------------------------|----------------------------------|

| DACS_Number of Bits []<br>B := 1.0                                | Oversampling Ratio []<br>R := 1024 | ADC Order []<br>n := 1              | Overload Voltage []<br>V := 0.75 |

| Integrator loop coefficients[]                                    | Fin maximum                        | Boltzman condt and Temp[]           |                                  |

| <b>a0</b> := 1.0 <b>a1</b> := 1.0 <b>a2</b> := 1.0 <b>a3</b> := 1 | <b>Fin</b> := $8 \times 10^3$      | <b>Kb</b> := $1.38 \times 10^{-23}$ | <b>Тенр</b> := 293               |

1st-order SDM, 1-bit -Quantizer, fs=16.138 MHz, Fin=8 KHz SNR- Equation

Maximum SNR

$$\mathbf{SNRpk} := \left[ (2)^{\mathbf{B}} - 1 \right]^{2} \cdot (2\mathbf{n} + 1) \cdot \left( \frac{\mathbf{R}}{\pi} \right)^{(2\mathbf{n}+1)} \cdot \mathbf{a0} \cdot \mathbf{a1} \cdot \mathbf{a2} \cdot \mathbf{a3} \cdot \left( \frac{3 \cdot \pi}{2} \right) \cdot \mathbf{V}$$

$\mathbf{SNRpk} = 3.672 \times 10^{8}$

+  $\mathbf{SNRdBpk} := 10 \cdot \log(\mathbf{SNRpk})$

Option III SigmaD ADC SNR(quantization)

CALCULATION

miki

DACS Number of Bits []

Oversampling Ratio []

ADC Order []

Overload Voltage []

B := 1.0

R := 128

n := 2

V := 0.75

Integrator loop coefficients[]

Fin maximum

Boltzman condt and Temp[]

**Fin** =  $8 \times 10^3$

**Kb** :=  $1.38 \times 10^{-23}$

2nd order SDM, 1-bit -Quantizer, fs=2.048 MHz, Fin=8 KHz SNR- Equation

Maximum SNR

$$\mathbf{SNRpk} := \left[ (2)^{\mathbf{B}} - 1 \right]^2 \cdot (2\mathbf{n} + 1) \cdot \left( \frac{\mathbf{R}}{\pi} \right)^{(2\mathbf{n}+1)} \cdot \mathbf{a0} \cdot \mathbf{a1} \cdot \mathbf{a2} \cdot \mathbf{a3} \cdot \left( \frac{3 \cdot \pi}{2} \right) \cdot \mathbf{V} = \mathbf{SNRpk} = 1.984 \times 10^9$$

#### In dB

a0 := 1.0 a1 := 1.0 a2 := 1.0 a3 := 1

$\textbf{SNRdBpk} \coloneqq 10 \cdot \textbf{log}(\textbf{SNRpk})$

**SNRdBpk** = 92.976

**Temp** := 293

# End Lecture 10

www.gigalogchip.com