Welcome to 7718 semester 1 2022 <u>Mixed Signal Electronic Circuits</u>

Instructor: Dr. Miki Moyal

Lecture 08

**DIGITAL TO ANALOG CONVERTERS**

- 1. Transfer Function

- 2. Mismatches in layout

- 3. Architectures Types and Examples

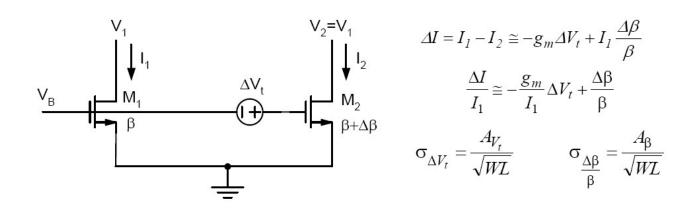

$$\sigma^{2}(I_{D}) = \frac{\beta^{2}}{2}(V_{GS} - V_{T})^{2} * \sigma^{2}(\Delta V_{T}) + I_{D}^{2} * \sigma^{2}(\frac{\Delta L}{L})$$

## **Mismatch in MOS Current Sources**

- Example

- W=500 $\mu$ m, L=0.2 $\mu$ m, g<sub>m</sub>/I<sub>D</sub>=10S/A, A<sub>Vt</sub>=5mV- $\mu$ m, A<sub>β</sub>=1%- $\mu$ m

$$\sigma_{\underline{\Delta I}}_{\underline{I_1}} = \sqrt{\left(10\frac{S}{A} \cdot \frac{5mV}{10}\right)^2 + \left(\frac{1\%}{10}\right)^2} = \sqrt{\left(0.5\%\right)^2 + \left(0.1\%\right)^2} = 0.51\%$$

#### אוניברסיטת **TELAVIV** עווע**ERSITY** דולאביב 7718-Lect 08

## Agenda

Transfer Function DAC architectures DAC Example Calibrations

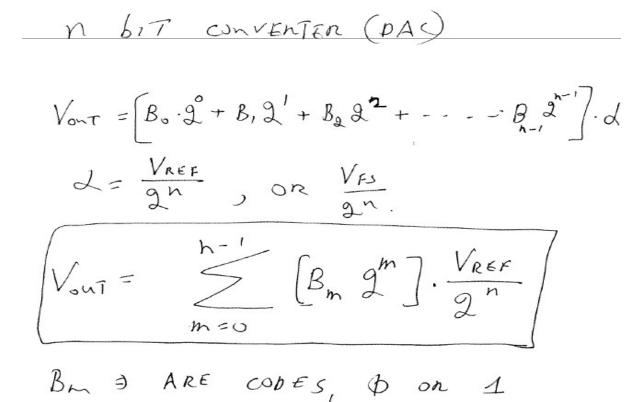

## **Transfer Function**

Equation (Binary weighted DAC)

Example

A 4 bit DAC having n=4 bits will have 4 digital inputs from 0000 to 1111. (0-15)

Vout (Fscale) = Vref(1/16) x [ B0 x1 + B1 x (2) + B2 x (4) + B3 x (8)]. = 15/16 x Vref

Can also be called "multiplying dac"

B's is a digital code, it is assumed a 0 value or a 1 value (digital codes)

Vref is a reference set by design to control the output range (supply range is the limitation, ~Vdd-0.6)

The minimum step is assume when B0=1 all other B's are 0! Is the Least significant bit (LSB).

## **Transfer Function (TF)**

A n bit DAC will have the following expression n is the resolution

Bo – is the lsb digital control Bn-1 – is the MSB digital control We set Vref, limited by process maximum range Semester / 1

January 12, 2023

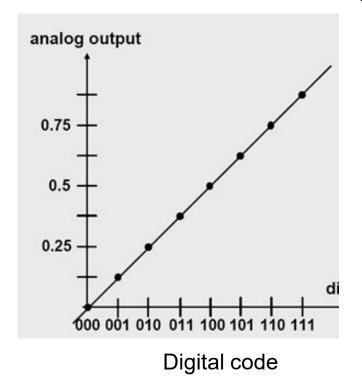

**Ideal TF plot**

Output = Digital Code x Vref (analog) Multiplication of analog value by Digital Fraction Fraction multiplication is done using Matched resistors, Current, or Capacitors

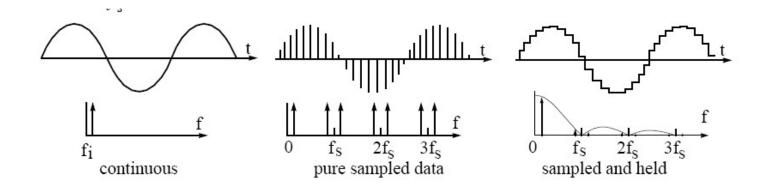

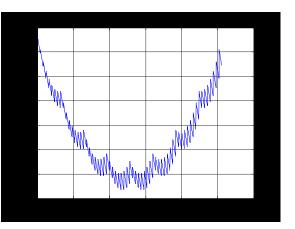

## **Frequency domain**

Source : analog Integrated Elect 2000

January 12, 2023

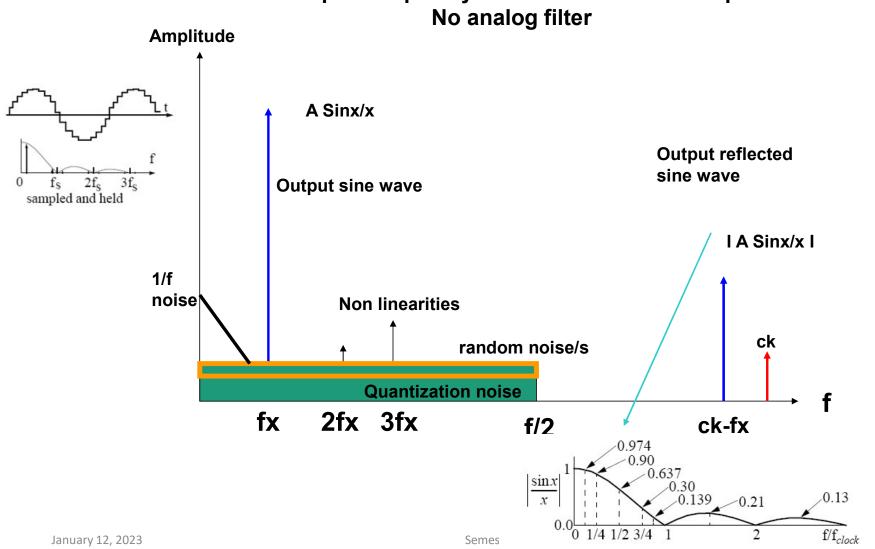

# DAC output Frequency domain – sine wave response

8

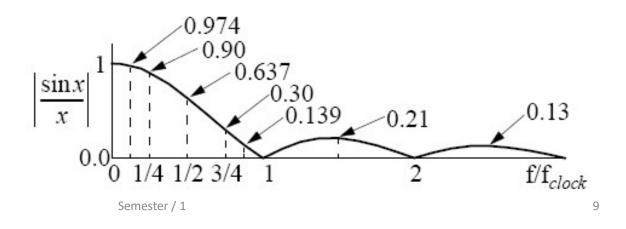

# **ISinx/xI** mean what !

Example:

If fin lies at 1/4 fs ! (fs=1MHz and fin=250KHz)

Pi x <sup>3</sup>/<sub>4</sub> = 135 deg.

Sin(135) / 3.14x3/4 = 0.707/2.355=0.3

January 12, 2023

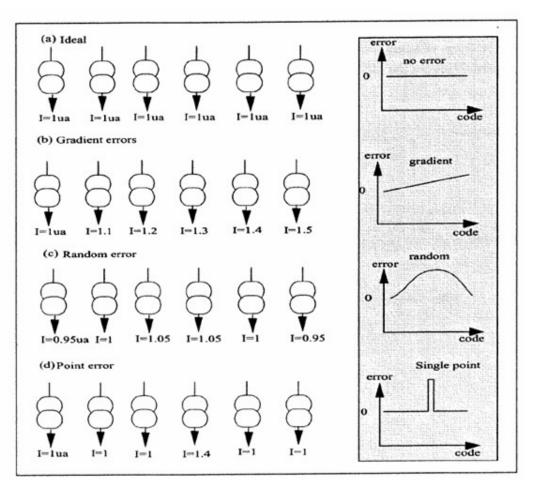

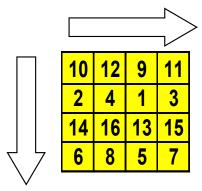

## Type of mis-matches

a) No error b) Gradient c) Random d) Single point

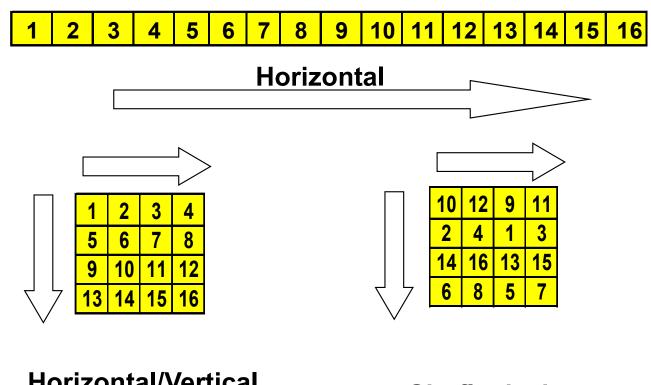

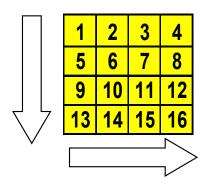

## **Horizontal/Vertical**

## Shufle design

## horizontal unit placement

## Horizontal/Vertical unit placement

January 12, 2023

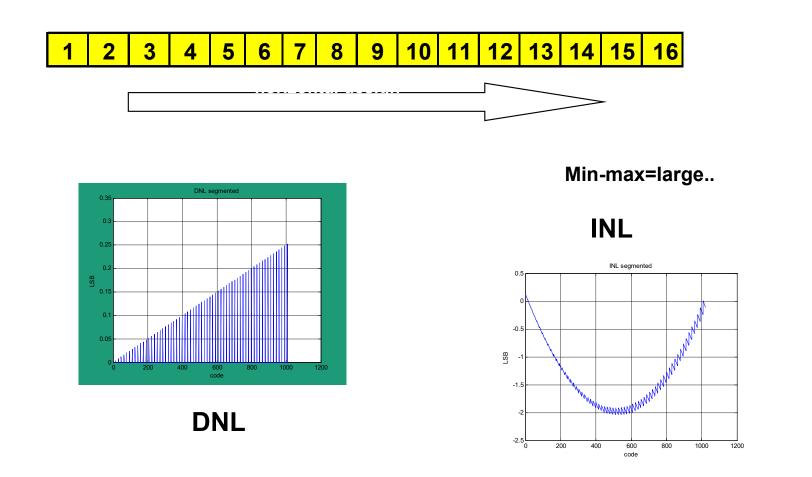

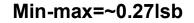

## Shuffle unit placement

Min-max=~0.25lsb

January 12, 2023

## dummies

| <u> </u> |    |    |    |  |

|----------|----|----|----|--|

| 10       | 12 | 9  | 11 |  |

| 2        | 4  | 1  | 3  |  |

| 14       | 16 | 13 | 15 |  |

| 6        | 8  | 5  | 7  |  |

| {        |    |    |    |  |

#### Keep background of edge unit identical Some goes to the extreem of 2 rows

January 12, 2023

## **DACs Architectures**

Voltage mode: R Ladder and R-String DAC The Basic R-2R DAC R and I DAC C DAC Current (steering) DAC

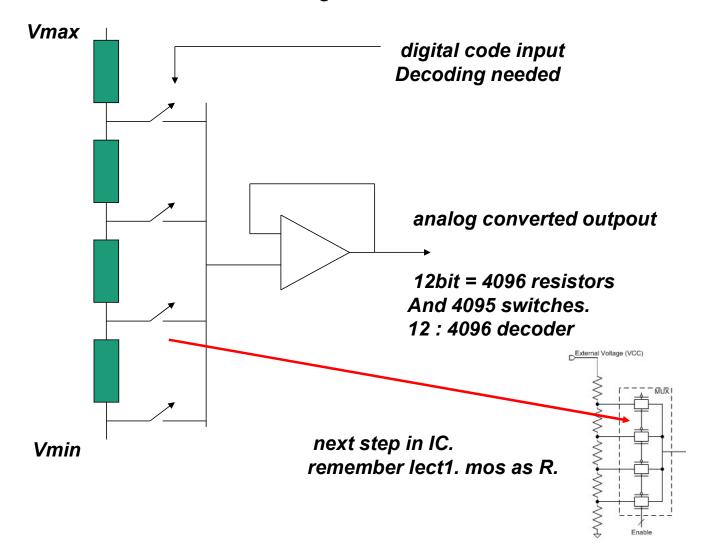

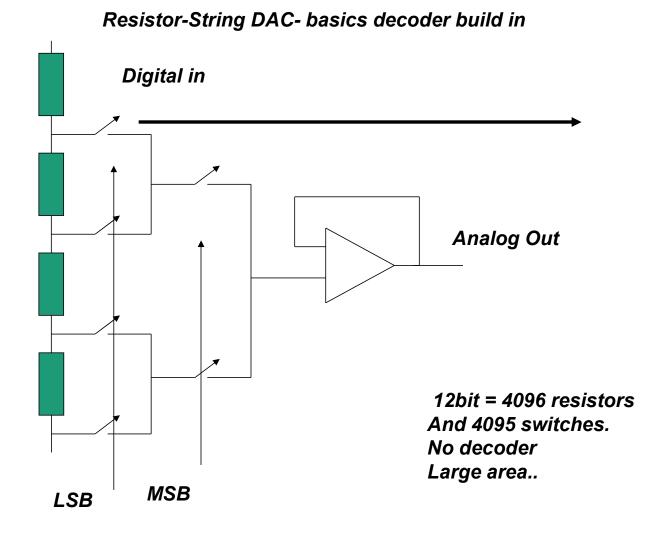

#### Resistor-String DAC- basics

Voltage mode: R Ladder and R-String DAC

#### Voltage mode: R Ladder and R-String DAC- Equations

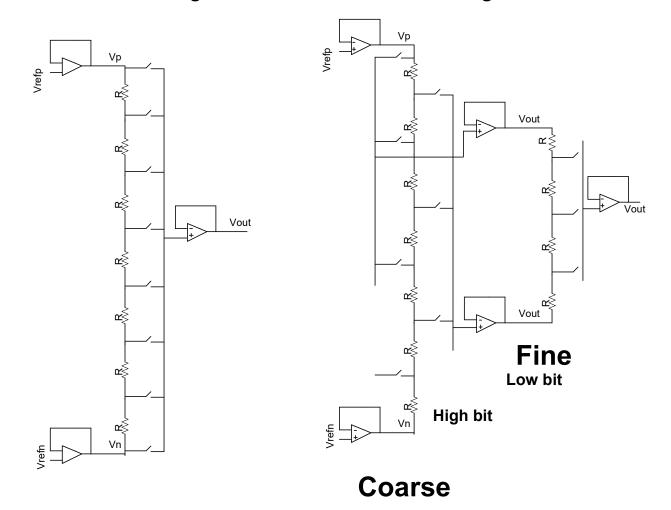

**R string** - Easy to implement in CMOS, "large" die size (In use up 8-10b) A switch and resistor, digital selection, decoding, can be done with switch tree.

**Multiple R-String** allow increase in resolution (<u>keeping monotonic</u>) With only doubling the R string. (Holloway 84) Need only 2N+1 resistors not 2 to the power of N.

**Speed is limited** by amplifier input capacitance switch resistance and opamp BW Op1 op2, and op3 offset is a draw back

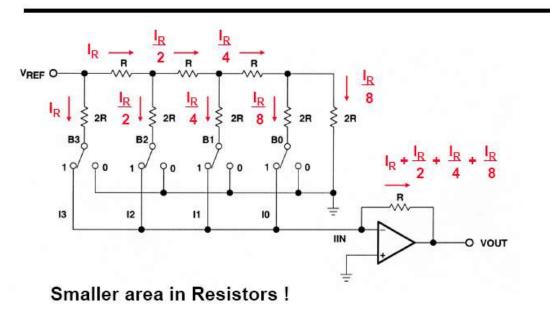

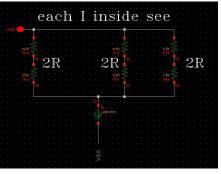

## THE BASIC R-2R DAC

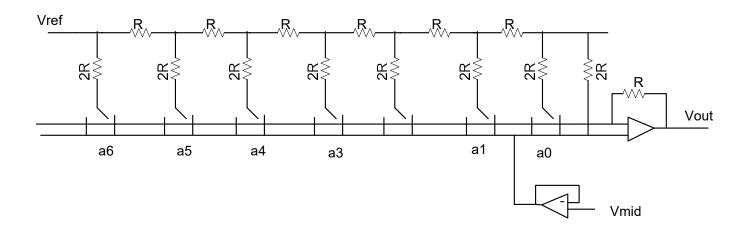

**R-2R DAC**

Willy Sansen 10-05 2013

*Motivation: lower area, 12b=25 resistors*

No guaranteed monotonic, bad offset sensitivity

Operation- unipolar output:

msb I(a6=H)= -Vref/2R only a6 goes H I(a5=H)= -Vref/4R Isb I(a0=H)= -Vref/128R only a0=H I total = -Vref/R – Vref/128R all switches to out=H

Bipolar output possible with an extra amplifier and the use of Vmid

## *R-2R key issues*

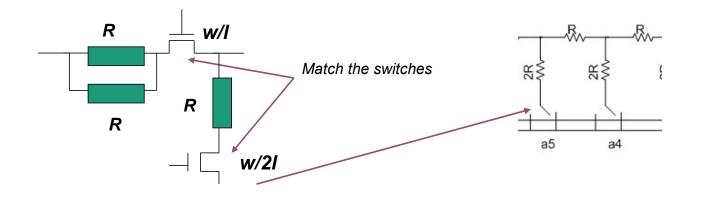

Very common architecture if thin film resistors are used (Cecil 74) Area efficient- Easy to increase resolution R-2R per bit Monotonic is not granted INL and DNL are closely coupled **Relatively Slow**

"rule of thumb" : Matching requirement for the n th bit in the i th bit

$\Delta R < \frac{R}{2^{n-i}}$

1) Switch resistance, Vgs voltage changes will effect mismatches

2) Problem: Output impedance changes and get multiplied by amplifier offset Looking from the other side (opamp side) R looking back form the amplifier vary with code.

can we Fix the impedance issue

## R-2R and I

#### Architectures for Nyquist High-Speed D/A converters:

#### · R-2R ladder:

- Area is reduced compared with resistor string

- Simple design: equal resistor R-2R blocks, switches and current sources

- · Fixed output impedance

- · Accuracy is limited by matching of resistors and current sources

- · Poor power efficiency

Source: R V Plasshe

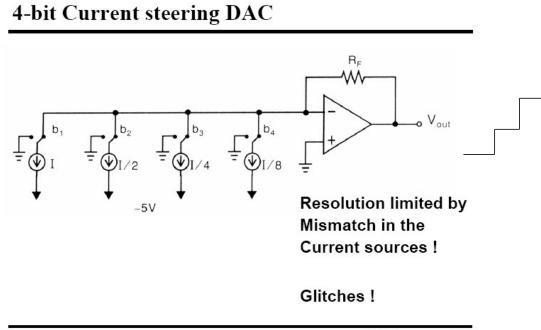

## **Current DAC**

Willy Sansen 10-05 2015

Limit: Thermal/1/f Noise of Idac, opamp (gmin), and Rf. Speed: Fast-- as opamp unity gain Band width.

## I dac with reference

Iref is generated using op Vout is only a function of code and Vref

Additonal objective (for future technology generations): Low operating voltage 1.8 V

| Number  | Sign +          | Twos            | Offset            | Ones         |

|---------|-----------------|-----------------|-------------------|--------------|

|         | Magnitude       | Complement      | Binary            | Complement   |

| +7      | 0111            | 0111            | 1111              | 0111         |

| +6      | $0\ 1\ 1\ 0$    | 0110            | $1\ 1\ 1\ 0$      | 0110         |

| +5      | $0\ 1\ 0\ 1$    | 0101            | $1\ 1\ 0\ 1$      | $0\ 1\ 0\ 1$ |

| +4      | 0100            | 0100            | $1\ 1\ 0\ 0$      | 0100         |

| +3      | $0\ 0\ 1\ 1$    | 0011            | $1 \ 0 \ 1 \ 1$   | 0011         |

| +2      | 0010            | 0010            | $1 \ 0 \ 1 \ 0$   | 0010         |

| +1      | 0001            | 0001            | $1 \ 0 \ 0 \ 1$   | 0001         |

| +0      | 0000            | 0000            | $1 \ 0 \ 0 \ 0$   | 0000         |

| $^{-0}$ | 1000            | (0 0 0 0)       | $(1 \ 0 \ 0 \ 0)$ | 1111         |

| -1      | $1 \ 0 \ 0 \ 1$ | 74.11           | 0111              | 1110         |

| -2      | $1 \ 0 \ 1 \ 0$ | 1110            | 0110              | 1101         |

| -3      | 1011            | 1101            | 0101              | 1100         |

| -4      | 1100            | 1100            | 0100              | 1011         |

| -5      | 1101            | 1011            | $0\ 0\ 1\ 1$      | 1010         |

| -6      | 1110            | 1010            | $0\ 0\ 1\ 0$      | 1001         |

| -7      | 1111            | $1 \ 0 \ 0 \ 1$ | $0\ 0\ 0\ 1$      | 1000         |

| $^{-8}$ |                 | 1000            | 0000              |              |

## **Glitch control** Coding schemes..:

Good around +/-0

•Offset Binary. Obtained starting to encode from the most negative number.

•Sign Magnitude. The MSB represents the sign, the others the absolute value.

• 1's Complement. Negative numbers are obtained complementing positive numbers.

• 2's Complement. Obtained from the offset binary complementing the MSB;

negative numbers equal to 1's complement plus one.

Lect 06

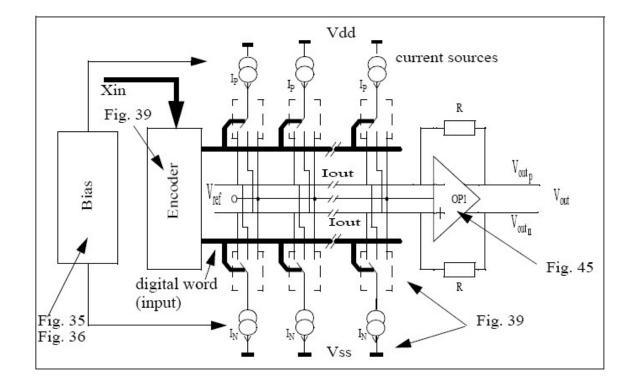

## DAC Differential Architecture

## DAC with ..- sign magnitude..

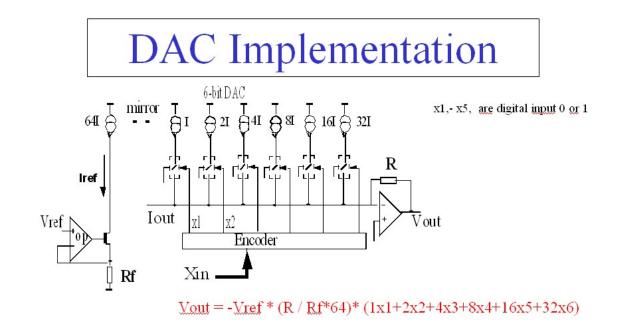

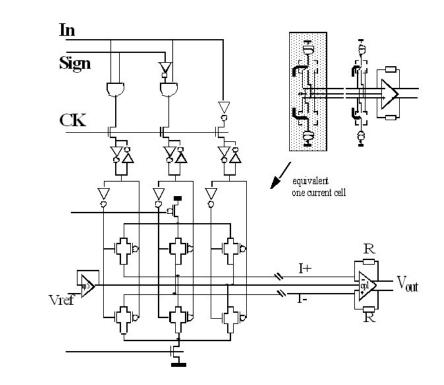

# LSB Implementation

- 64 units

- Sign input is for current direction

- CK is to latch the data

- Example:

- if  $\mathbf{In} = 0$ , Vout=0

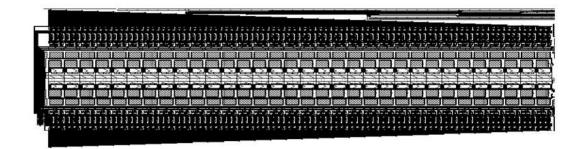

# DAC Layout

- Hand layout to allow "shielding" of analog from digital

- Iout lines are in the middle

- Digital on the outside

- Area:  $Core < 0.6 \text{ mm}^2$  (total <1)

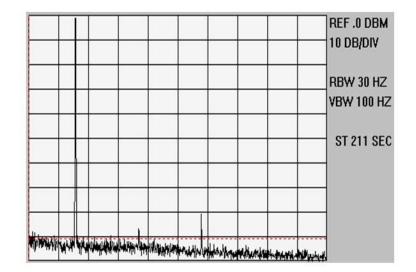

## Measured Results

## Transmitter Harmonic

WITHOUT DYNAMIC AVERAGING

2rd Harmonic at - 87dB 3nd Harmonic at - 78dB 5th Harmonic at - 87dB

Output is valid only part of the time (switched) may need Hold switch Marching of capacitors set the INL / DNL

Limit: Noise KT/C, glitches Speed: Fast-- as Ron of switch, vref settling, and and C/2 n time constant.

Could be non Monotonic- in transitions Simple decoder

> "best" for speed => lout time constant

- 001 00000001

- 010 00000011

- 011 000000111 always one change

- 100 000001111

Source: B. Murmann Stanford

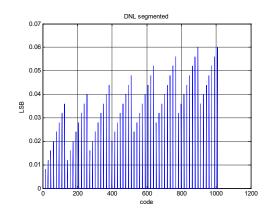

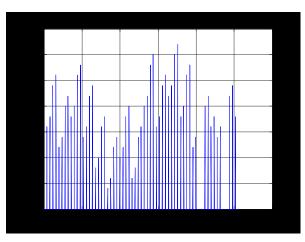

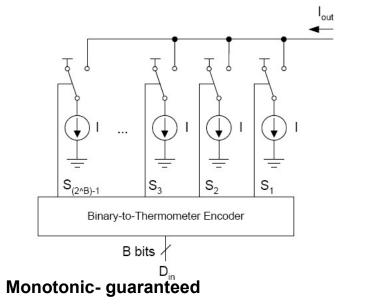

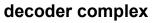

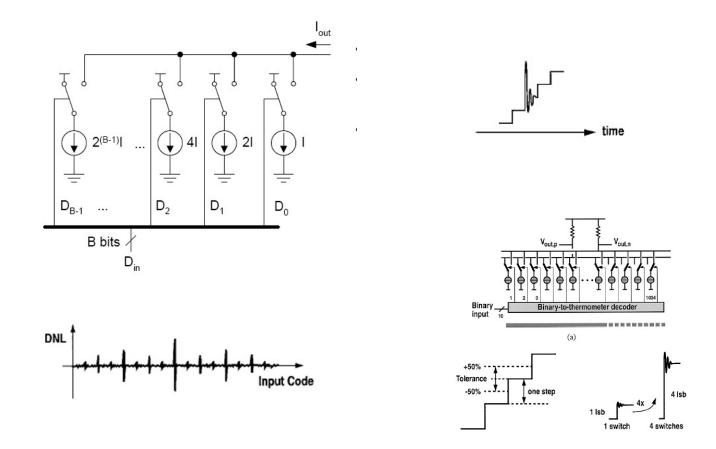

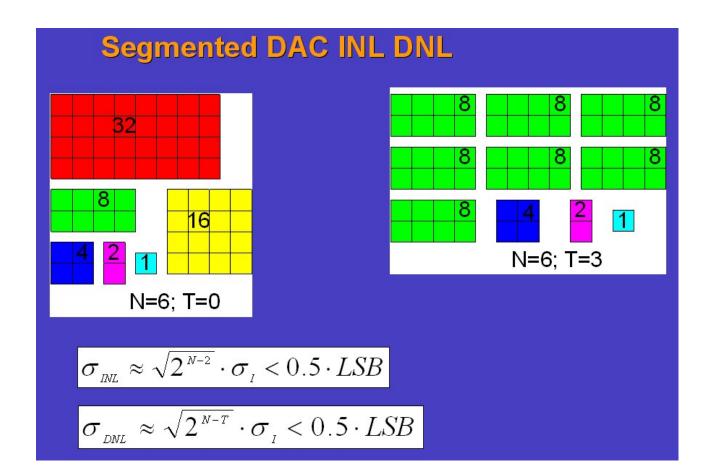

## **Binary Vs. Thermometer - mismatch**

FOR THE SAME AREA INL – THE SAME DNL – BIG DIFFERENE Figure out the optimum place: how many binary bits and how many segmented bit

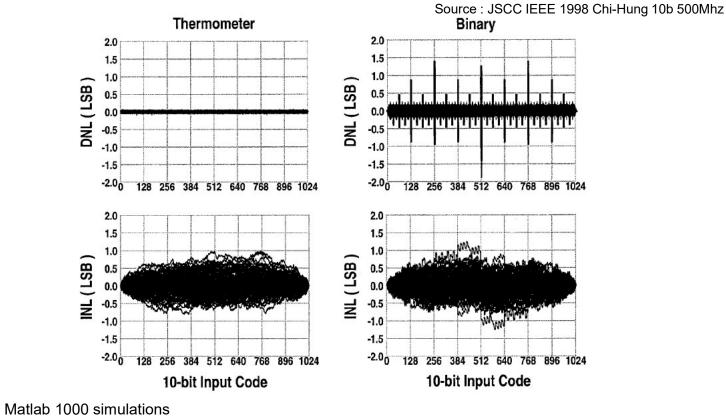

## **DAC Response**

## **Glitches and INL in Binary dac**

If the glitches scale with code (and capacitance is linear) - Linearity is good

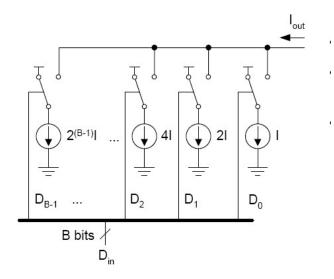

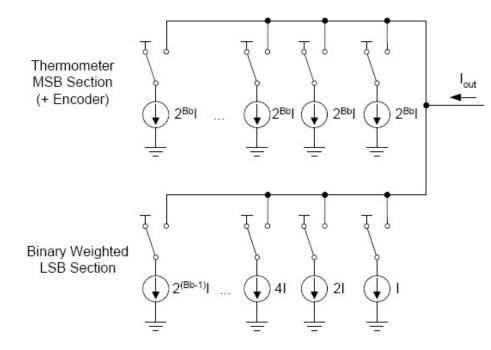

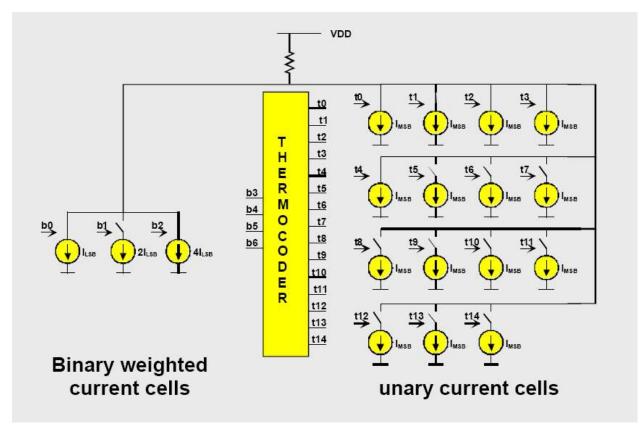

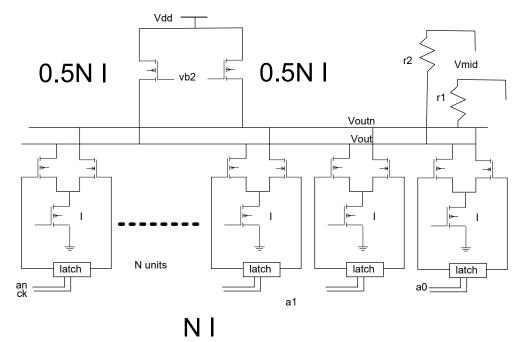

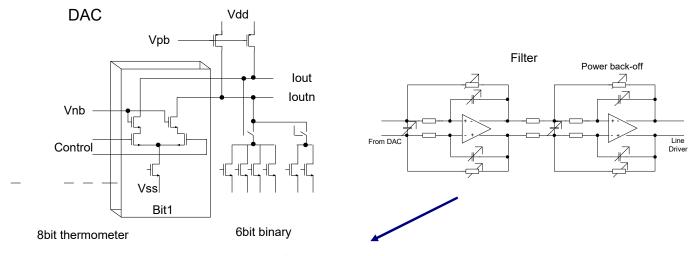

## **Combined I dac - segmented**

- Binary weighted section with B<sub>b</sub> bits

- Thermometer sectior with B<sub>t</sub> = B-B<sub>b</sub> bits

- Typically  $B_t \sim 4...8$

- Reasonably small encoder

- Easier to achieve monotonicity

Source: B. Murmann Stanford

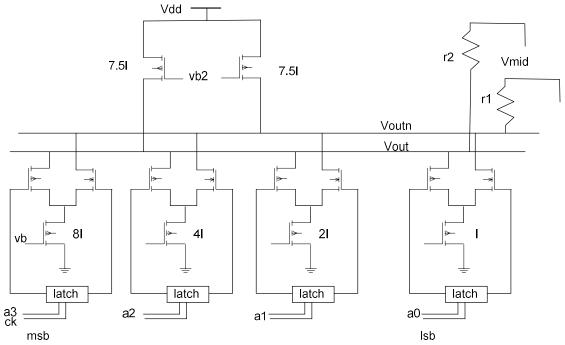

## **Current (steering) DAC- removed opamp**

Source : G. Gielen, K.U.L Leuven

2 option of DAC arrangements

## **Current source implementation**

#### STATIC PERFORMANCE In Current-Steering D/A Converters

#### DNL in binary D/A converters:

Worst case DNL for the midcode transition (MSB):

$$\sigma^{2}(\Delta I) = \sigma^{2} \left( 2^{N-1} i_{0} - \left( 2^{N-1} - 1 \right) i_{0} \right) = \left( 2^{N} - 1 \right) \sigma^{2}(i_{0}) \Rightarrow$$

$$DNL^{\max} = \frac{\sigma(\Delta I)}{i_{0}} = \sqrt{2^{N} - 1} \frac{\sigma(i_{0})}{i_{0}} \text{ in LSB units}$$

#### DNL in thermometric D/A converters:

DNL limited by the LSB a single  $i_{\theta}$  source is connoted or disconnected from adjacent code to code transitions:

$DNL^{\max} = \frac{\sigma(\Delta I)}{i_0} = \frac{\sigma(i_0)}{i_0}$  in LSB units

DNL < 0.5 LSB is guaranteed for as much as a 50% precision in the  $i_0$  sources

High-Speed CMOS D/A Converters, May 2002

## Comparison

|                                   | Thermometer                            | Segmented                           | Binary<br>Weighted              |

|-----------------------------------|----------------------------------------|-------------------------------------|---------------------------------|

| σ <sub>INL</sub><br>(worst)       | $\cong \frac{1}{2}\sigma_u \sqrt{2^B}$ |                                     |                                 |

| σ <sub>DNL</sub><br>(worst)       | $\cong \sigma_u$                       | $\cong \sigma_u \sqrt{2^{B_b+1}-1}$ | $\cong \sigma_u \sqrt{2^B - 1}$ |

| Number of<br>Switched<br>Elements | 2 <sup>B</sup> – 1                     | $B_b + 2^{B_t} - l$                 | В                               |

Source: B. Murmann Stanford

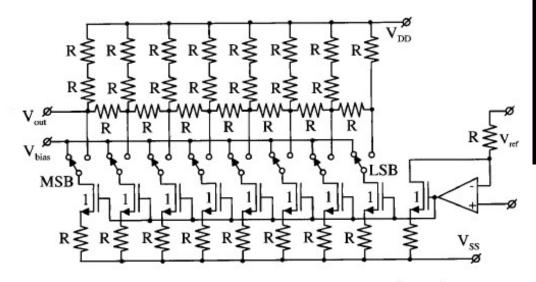

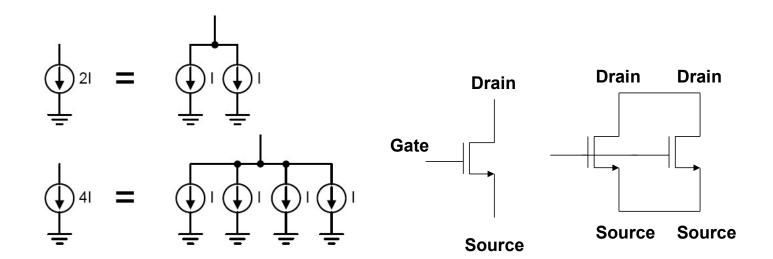

### Differential I/2I mode DAC TYPES

## **Binary Weighted**

### Use twice the current on the bottom But only n ch switches

#### Very Fast

Compact N latches ( but need to be sized up) Linearity limited by MSB DNL spikes: in some code transitions

## Thermometer

Current source matching relaxed Each stage is LSB equivalent in contribution For N bit, 2 to power of N latches, unit cells, wires Silicon area is large, depend on marching and routing Power supply grounding is important I deal: Can combine with Binary approach and leave some MSB as Segmented

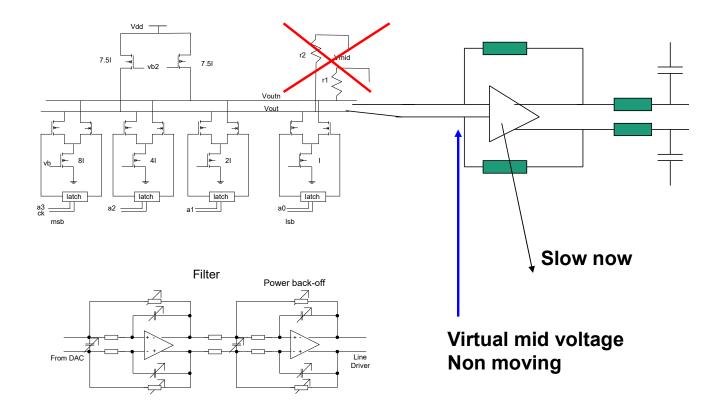

## DAC with reduced Rout effect and filter

Fix the output impedance variations And add the « out of ban » noise reduction filter

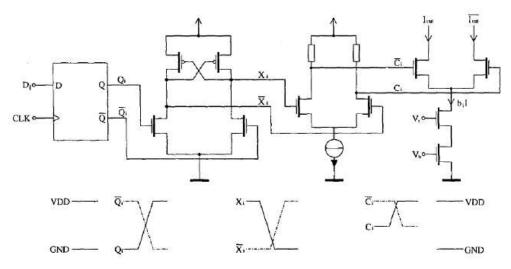

## **Pre driver**

### LATCH AND SWITCH Minimization of glitches

- · Non symmetrical crossing point: reduces current source drain spike

- Reduced clock swing: sets on-voltage for cascoding bias and reduces clock feed-through

L. Sumanen, et al, "A 10-bit High-Speed Low-Power CMOS D/A Converter in 0.2mm2", Proc. of ICECS, 1998

High-Speed CMOS D/A Converters, May 2002

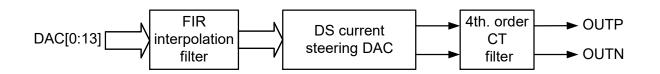

## Dac to output path

Fillter to reduce out of band noise Set poles to alfa above maximum BW

Lect 06

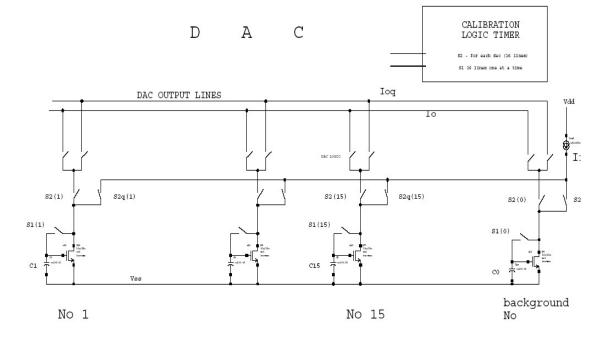

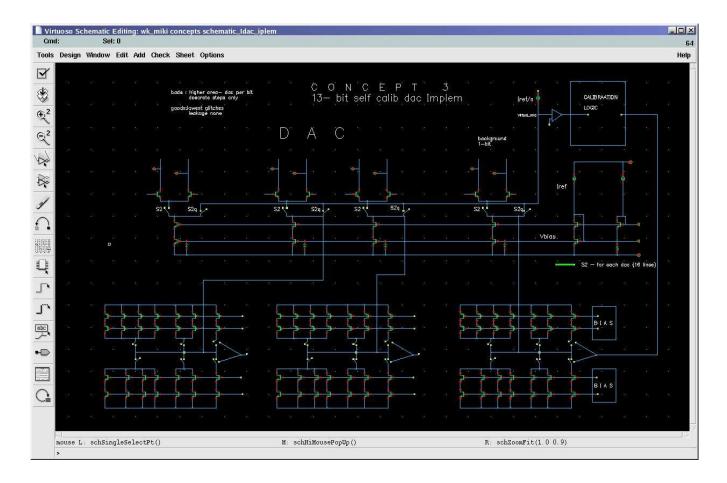

# **Calibration Methods**

Make all I the same

Add error I

Dynamic Averaging

# **Calibration Method 1**

## **Calibration Method 1**

# End lecture 08