Welcome to 0510.7720.01 Winter semester 2021 <u>Mixed Signal Electronic Circuits</u> Instructor: Dr. M. Moyal

Lecture 6 and 7- recorded for: may 13<sup>th</sup> and 20 2021..

**Comparator: Operation and Design**

Quick review on analog circuits basics

- **Comparator Basics**

- □ Architectures

- **□** Error Sources

- Comparator Examples

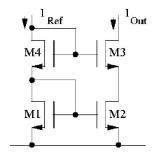

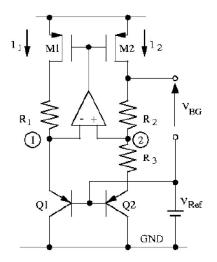

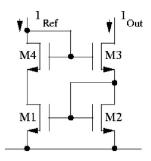

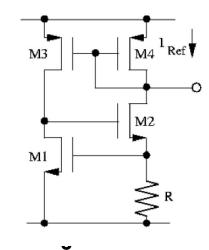

#### Current sources- the heart of Analog Ics..-Video discussions..

#### Cascode/cascade

Improved Wilson Current Mirror

For the project assignment---convert the digital back to numbers..

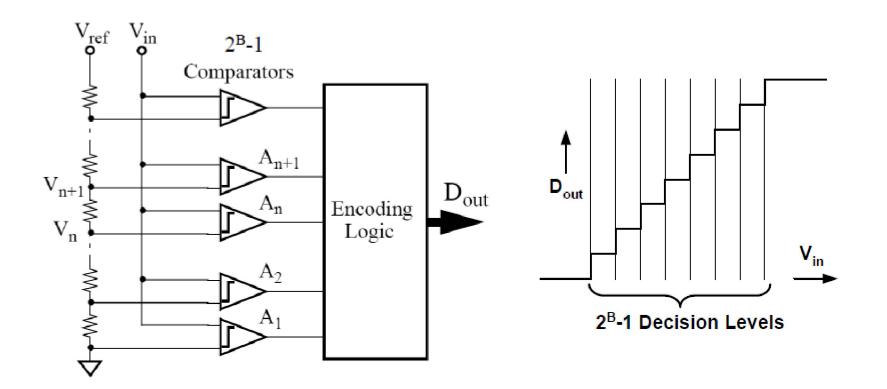

# Flash ADC

Comparator:

Non Sampled

□ Sampled

**□** Error in Comparators

Basic Analysis

□ Architectures

□ Special topics – Calibrated and differential

# **Comparator**:

□ A Link from Analog to Digital – Quantizer

# Definition:

Compares between 2 or more inputs and produce a digital value high or low- "Its a 1 bit ADC !"

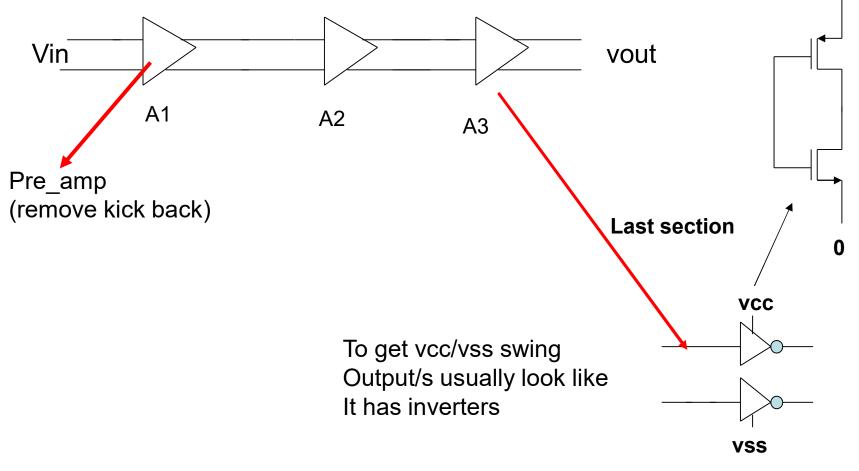

### Structure:

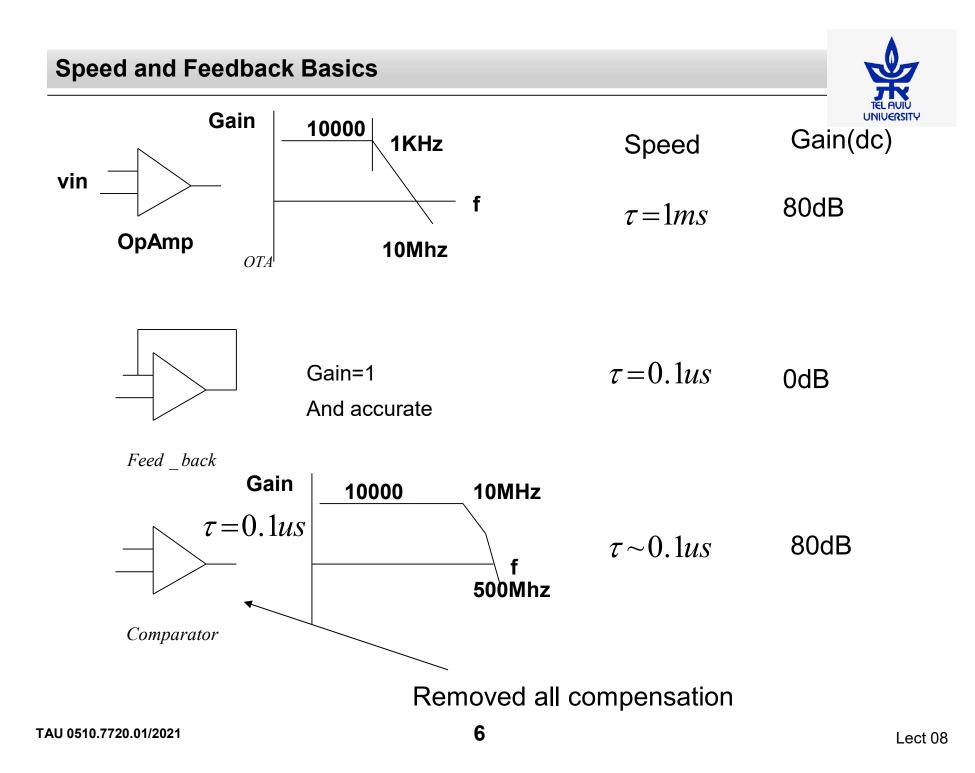

□ A chain of gain stages (no feed back-unlike amplifier)

□ It is used in an "open Loop" configuration to achieve fast digital response (opamps are slow and big)

Vcc

# □ Non Sampled: Continuous Time (CT)

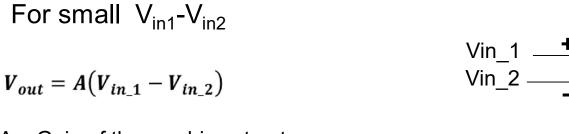

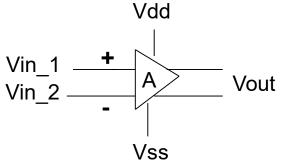

□ Output is gain time input differences:

□ slow because internal nodes need to be recovered

A = Gain of the combine structure

For all  $V_{in1}$ - $V_{in2}$   $V_{out}$ =clamp at either supply

#### Ideal

$V_{out} = A(V_{in_1} - V_{in_2}) \rightarrow \text{results fall between supplies (realistically its exponential)}$

$$V_{out} = V_{dd} \quad if \ A(V_{in_{1}} - V_{in_{2}}) > V_{dd} - V_{ss}$$

$$V_{out} = V_{ss} \quad if \ A(V_{in_{1}} - V_{in_{2}}) < V_{dd} - V_{ss}$$

#### **Mathematical Descriptions with Noise**

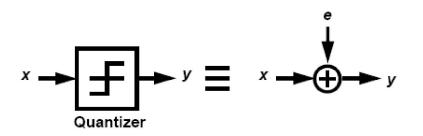

exact model if e is defined properly ex. *y*=*sgn*(*x*), then *e*=*y*-*x*=*sgn*(*x*)-*x*

becomes an approximation when we claim noise is independent

Important model in Sigma Delta ADCs

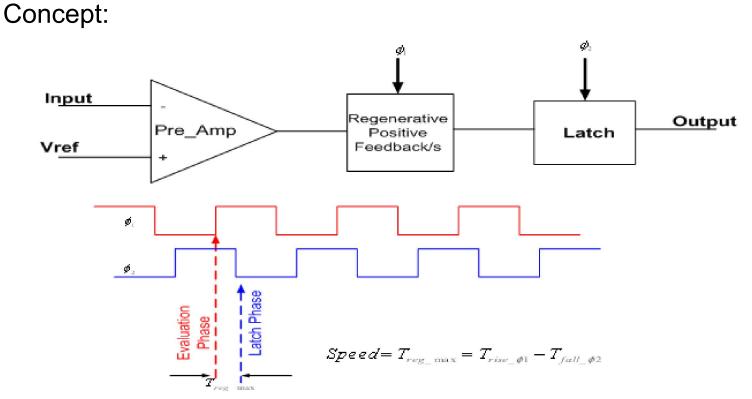

#### □ Sampled Comparator:

- □ Much faster

- □ clamp high gain stages

- Need clock or digital signal

# Errors in Comparators: Gain Offset Meta State Speed Kick Back Noises and supply noise

- Input Offset It is the voltage that must be applied to the input to obtain the crossing point between low and high logic level

- Vout = A x Vindiff, vss<Vout<Vdd A=1000, time is also a factor</li>

- <u>Sensitivity</u>- It is the minimum voltage or current that produces a consistent output signal within the expected comparison time- <u>Meta state</u>

- <u>Comparator response time</u> It is minimum time interval required to achieve the proper logic output as a response to the minimum input step

- Overdrive recovery time When the input signal is pretty large the gain stage saturates to the positive or negative rails quickly. If the input stage become small, the gain stage takes some time to react and generates the voltage required to produce the output voltage

- <u>Kick back input noise</u> Caused in evaluation state due to transition response: Switching noise

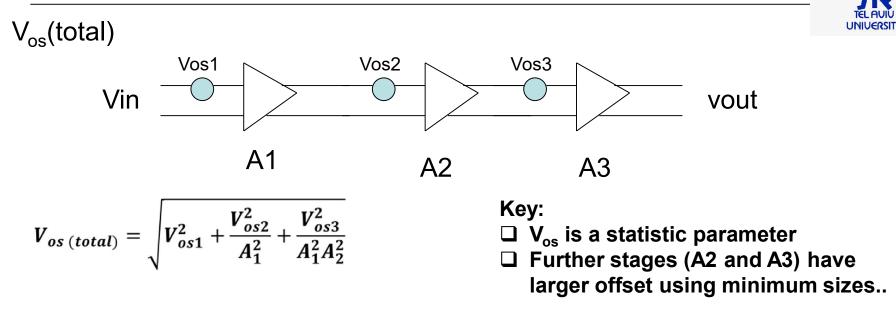

#### **Offset and Gain – Basics in Comparator**

#### Example: 8 bit ADC

for 8 bit with  $V_{fs}=0.5v$ ,  $V_{dd}=1v$  at 1/10LSB = A1 x A2 x A3 required ~ 5000  $\rightarrow$  (1v/(0.5/255 x 10) If: Vos1=2mv, vos2=10mv, vos3=20mv If we take: A1=10mv A2=25mv A3=20mv

$$V_{os\,(total)} = \sqrt{2^2 + \frac{10^2}{10^2} + \frac{20^2}{10^2 25^2}} = 2.23 mV$$

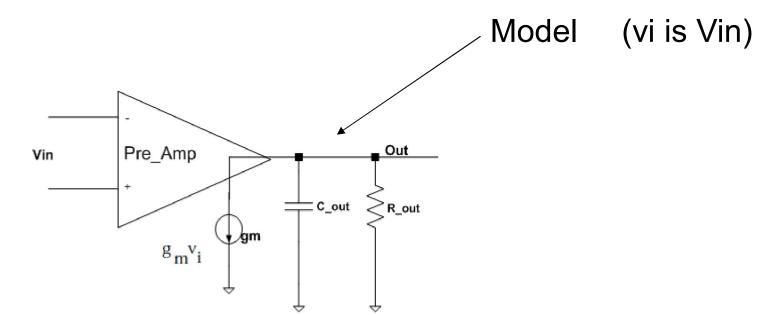

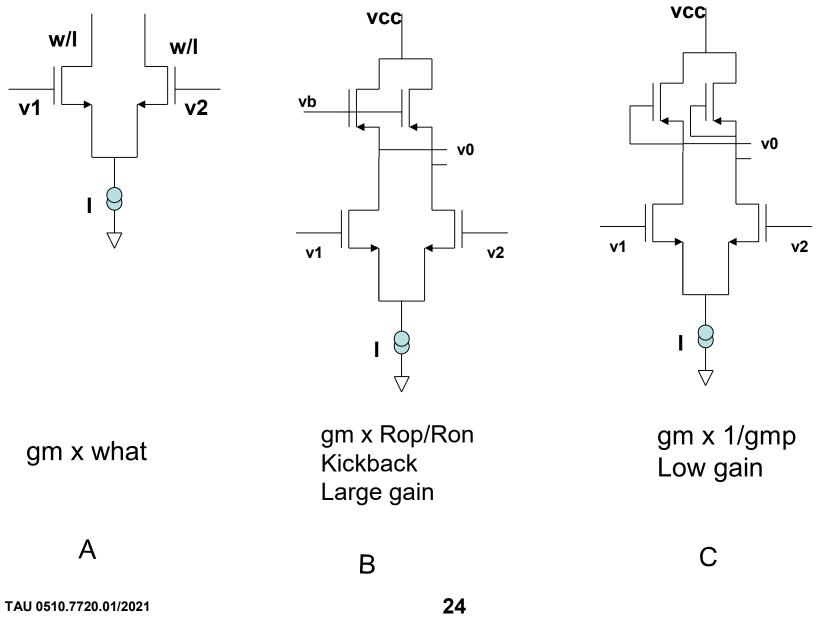

## Gm Rout ... diff stage..

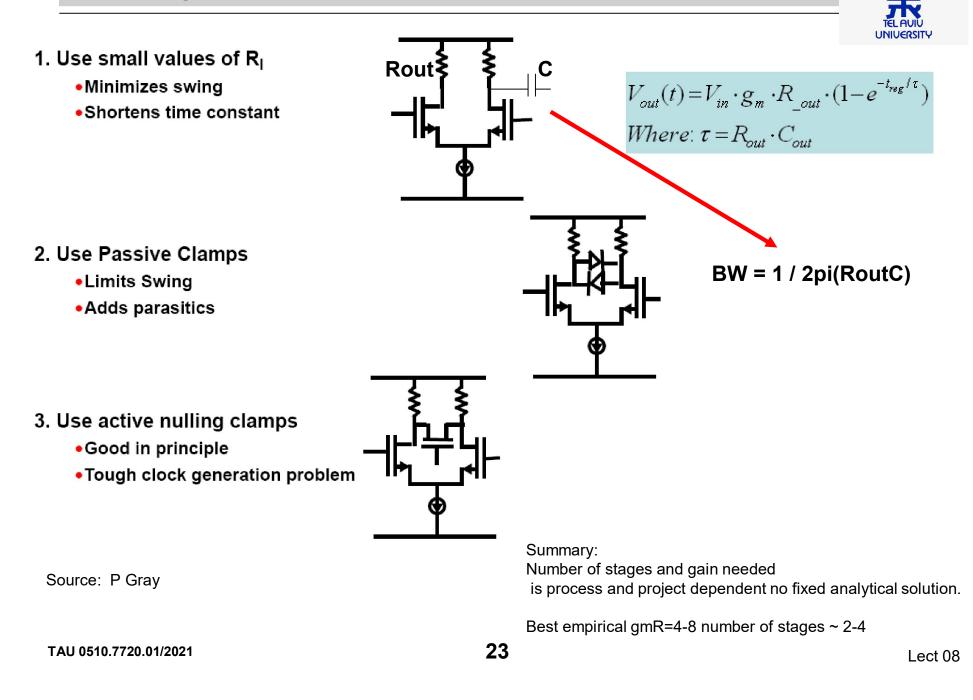

#### **Basic Analysis – Non Sampled – Non Latched**

$$V_{out}(t) = V_{in} \cdot g_m \cdot R_{out} \cdot (1 - e^{-t_{reg}/\tau}) \qquad g_m = \frac{I}{V_{in}}$$

Where:  $\tau = R_{out} \cdot C_{out}$

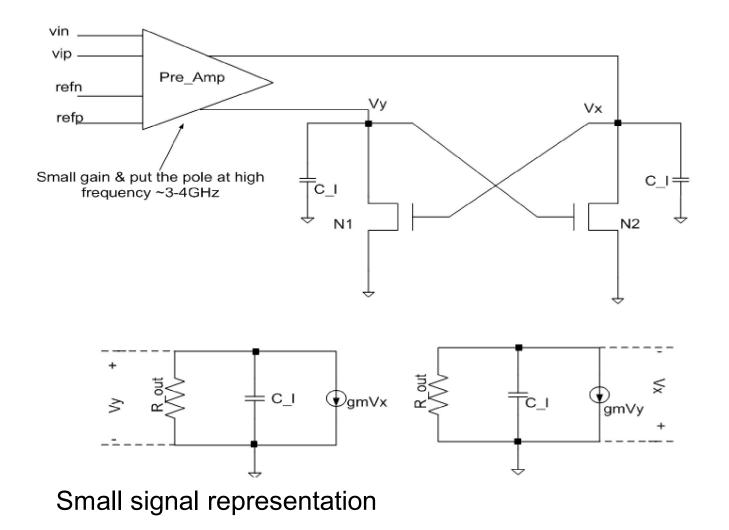

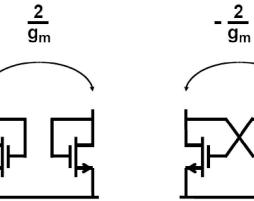

#### With Positive Feedback – Sampled

$$g_{m} \cdot V_{y} = -C_{L} \cdot \frac{dV_{x}}{dt} - \frac{V_{x}}{R_{out}} \qquad g_{m} \cdot V_{x} = -C_{L} \cdot \frac{dV_{y}}{dt} - \frac{V_{y}}{R_{out}}$$

$$\begin{cases} \tau \cdot \frac{dV_{x}}{dt} + V_{x} = -A \cdot V_{y} \\ \tau \cdot \frac{dV_{y}}{dt} + V_{y} = -A \cdot V_{x} \end{cases}$$

$$\Rightarrow \text{ where } \qquad \tau = R_{out} \cdot C_{L}$$

$$A = g_{m} \cdot R_{out}$$

$$T \cdot \frac{d(\Delta V)}{dt} = \Delta V(A - 1)$$

$$\Delta V = \Delta V_{0} \cdot e^{\frac{A - 1}{\tau}} \approx \Delta V_{0} \cdot e^{\frac{g_{m}}{C_{L}}}$$

$$\frac{\Delta V = \Delta V_{0} \cdot e^{\frac{A - 1}{\tau}} \approx \Delta V_{0} \cdot e^{\frac{g_{m}}{C_{L}}}$$

$$\frac{A - 1}{\tau} = \frac{g_{m} \cdot R_{out} - 1}{R_{out} \cdot C_{L}} \approx \frac{g_{m}}{C_{L}}$$

#### Band width reduction

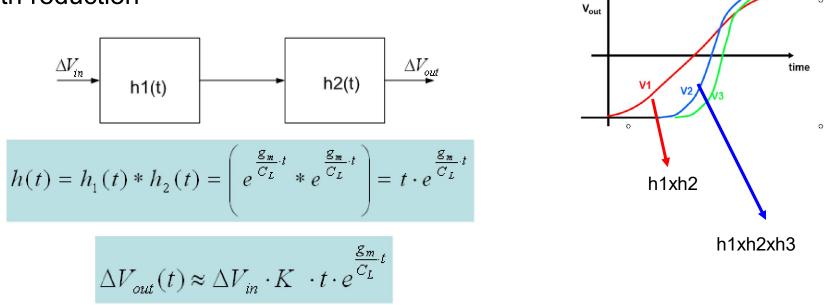

#### Note: if we have n-stages of the regenerative feedbacks then

$$h_{n}(t) = h_{1}(t) * h_{2}(t) \cdots * h_{n-1} * h_{n} = \left(e^{\frac{g_{m}}{C_{L}}t} * e^{\frac{g_{m}}{C_{L}}t} \cdots * e^{\frac{g_{m}}{C_{L}}t} * e^{\frac{g_{m}}{C_{L}}t}\right) = \frac{t^{n-1} \cdot e^{\frac{g_{m}}{C_{L}}t}}{(n-1)!} \qquad v_{oN} = \frac{\omega_{u}^{N}}{s^{N}} v_{in}$$

TAU 0510.7720.01/2021

$$\int_{0}^{+} v_{in} \frac{f_{in}}{f_{in}} \frac{g_{m}v_{in}}{f_{in}} \frac{f_{in}}{f_{in}} \frac{$$

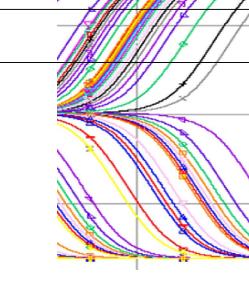

#### Meta Stability in Comparator

- Meta-stability is a potentially catastrophic event that can occur when asynchronous inputs and regenerative/flip-flops are used

- Meta-stable outputs are not logic high or logic low and cause delays and system failures

- Meta-Stability is a probabilistic event, because the difference between the input signal and the reference voltage is a random variable

- The smaller the difference between the input signal and reference voltage, the longer the decision time required. On the limit the decision time can approach infinity

# Analytical Derivation of Meta-Stability & Mean Time To Failure (MTF)

The probability event given following: where t is the actual comparison time, T is the allowed time

$$\Pr(t > T) = e^{\left(-\frac{A}{\tau} \cdot T\right)} = e^{-\frac{g_m}{C_{out}} \cdot T}$$

If one can have a collection of N such comparators all clocking at a frequency fs, then one can found MTF following

$$MTF \approx \frac{e^{\frac{A}{\tau} \cdot T}}{N \cdot f_s} = \frac{e^{\frac{\mathcal{B}_m}{\mathcal{C}_{out}} \cdot T}}{N \cdot f_s}$$

~ Set it for > month

• Example: 6-bit, 500MHz Flash ADC,  $T_{max}=T_s/2=1ns$ ,  $\tau_u=1/(2\pi \cdot 5GHz)=32ps$ ,  $A_v=3$ ,  $V_{FS}=0.5V_{DD}$

$$P(Error) = \frac{2}{3} \left( 2^6 - 1 \right) \cdot e^{-1000/32} \cong 10^{-12}$$

Mean time to failure (MTF)

$$MTF = \frac{1}{P(Error) \cdot f_s} = \frac{1}{10^{-12} \cdot 0.5 \cdot 10^9} s = 2000s \cong 33 \text{minutes}$$

source: Prof. Murmann stanford

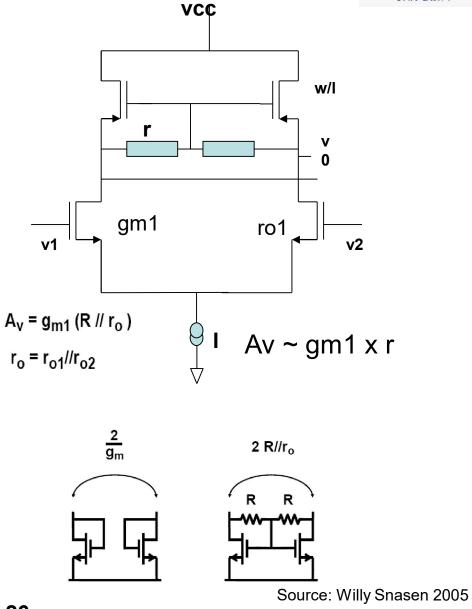

#### Front Stage Architectures- with Resistors

#### **Input Stage: Architectures Options - Using PMOS**

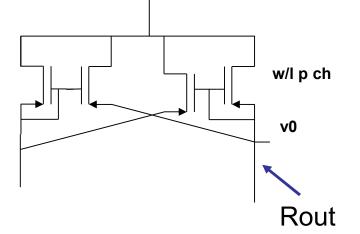

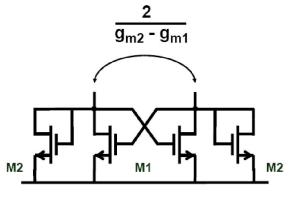

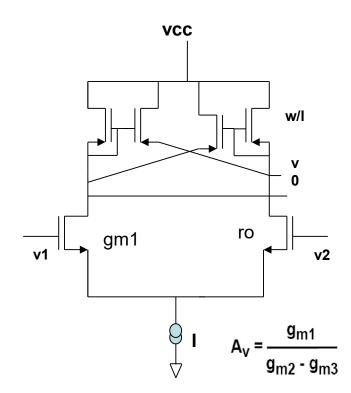

#### Added Feedback to Load

positive feedback to raise Rout

Effective rout =infinite

#### **Input Stage: Architectures Options**

Lect 08

AV ~ gm1 x ro

# **Comparator Examples**

#### Simple

Good for low supply Reset switch to ground Kick back

#### Question can the outputs (inverter) swing to Vss ?

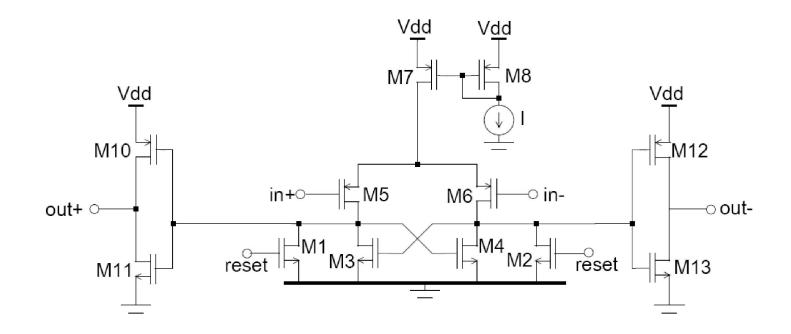

#### Differential Input Two Stage Comparator Option (no pre\_amp)

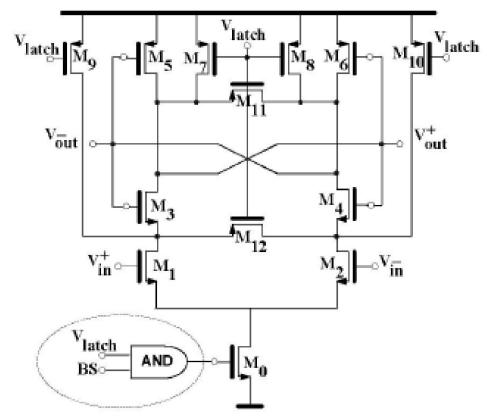

Fig. 5: High speed comparator and its switching circuit

A Power-Efficient 1.056 GS/s Resolution-Switchable 5-bit/6-bit Flash ADC for UWB Applications

Jun-Xia Ma, Sai-Weng Sin, Seng-Pan U<sup>1</sup>, R.P.Martins<sup>2</sup>

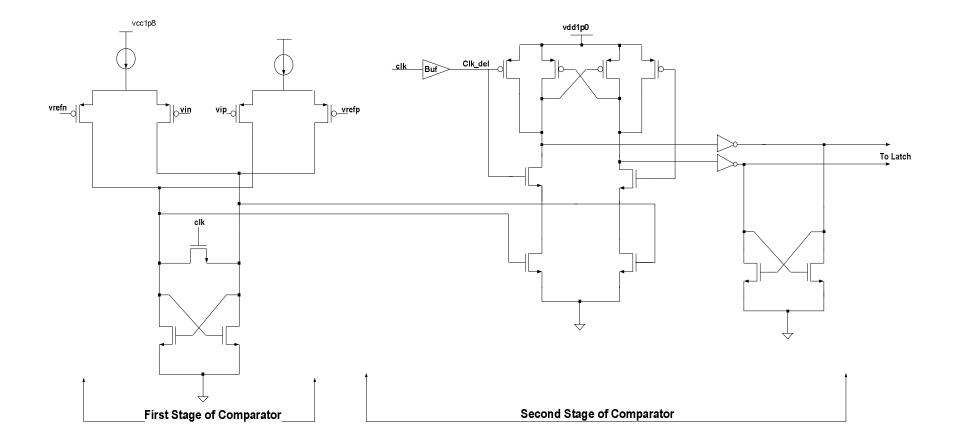

# Special Topics – Calibrated and differential Architectures examples

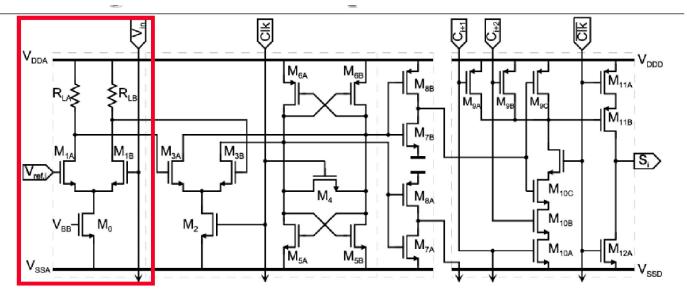

- Pre-amplifier [M1a,M1b]

- Differential Pair with resistive load

- Reduce Kick-back noise

- Reduce Input Referred Offset Comparator

Source: Esat-Micas esscirc00

# **Offset Calibration of Comparators:**

#### Why? $\rightarrow$ Main reason lower input capacitance

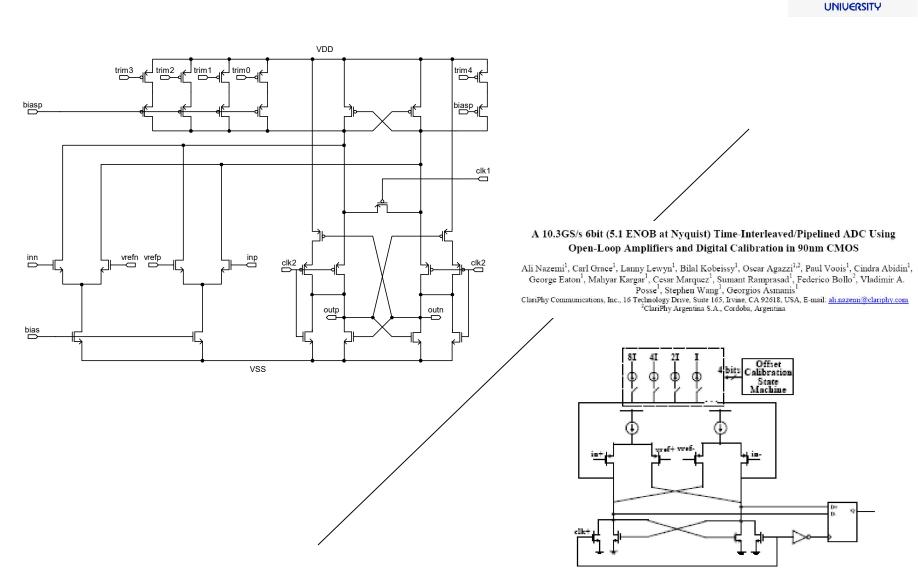

#### **Differential – Latched with Calibration Differential**

Comparator schematic with digital offset calibration.

# **End Lecture 8**

Additions

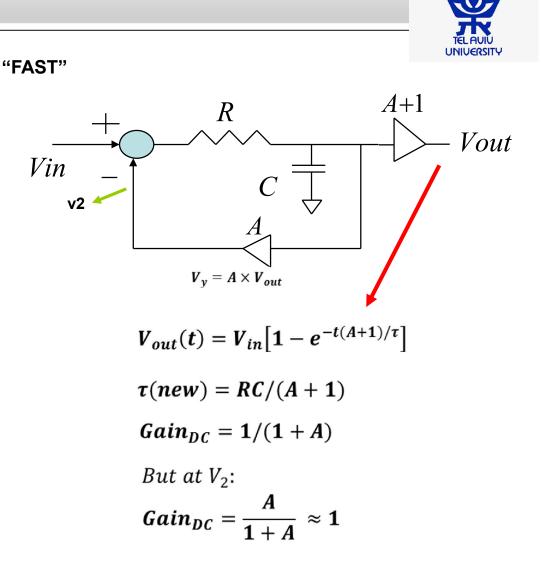

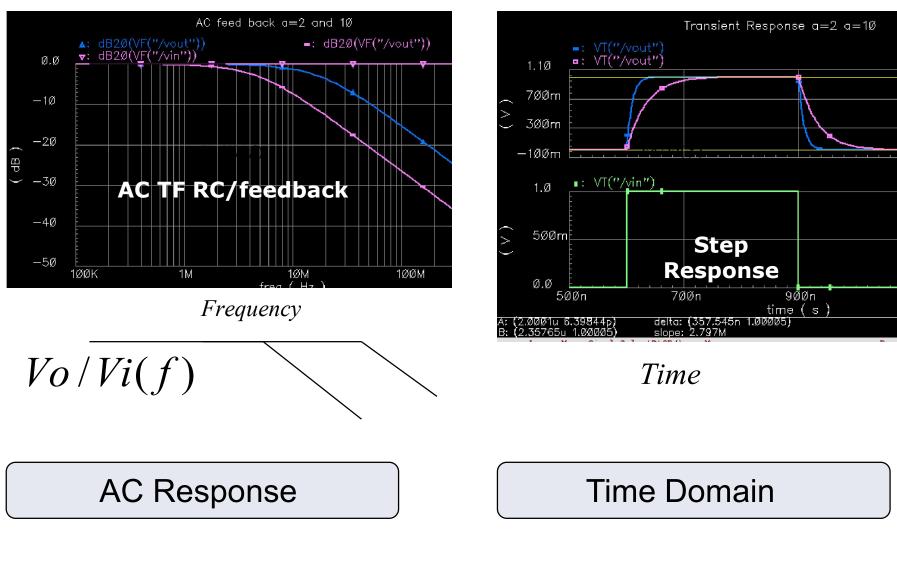

#### **Basic Feedback to Boost BW**