Welcome to 046188 Winter semester 2012 <u>Mixed Signal Electronic Circuits</u> Instructor: Dr. M. Moyal

### Lecture 5a

Cont. Mismatches in Mixed Signal Circuits

Mismatches in CMOS devices.

www.gigalogchip.com

## Summary lect. 2-4

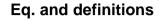

$$SNR = \frac{Signal Power}{Total Noise Power}$$

$SNDR = \frac{Signal Power}{Noise and Distortion Power}$

$ENOB = \frac{SNDR(dB) - 1.76dB}{6.02dB}$

$SFDR = \frac{Signal \ Power}{Largest \ Spurious \ Power}$

$THD = \frac{Total \ Distortion \ Power}{Signal \ Power}$

# MISMATCHES

One of the most critical parameters in Mixes signal design.

Mostly ignored with normal simulators

## Mismatches- modelling-"Pelgrom rule"

#### MISMATCHING In Current-Steering D/A Converters SOLID-STATE CIRCUITS, VOL. 24, NO. 5, OCTOBER 1989 IFFE JOURNAL OF ro equal Matching Properties of MOS Transistors MARCEL J. M. PELGROM, MEMBER, IEEE, AAD C. J. DUINMAIJER, AND ANTON P. G. WELBERS 'Random' mismatch. 'Systematic' mismatch Transistor sizing Layout techniques Av $V_T$ $\sigma_{\beta}$ $S_{\beta}^2 D^2$ $\mathcal{V}$

First test:

Is it a current source mode ? Is it a voltage mode device ? Is it a switch ?

Mixed signal design must address:

Can we ignore/neglect the error ?

If not can we "calibrate" or fix the errors ?

Process deviation: threshold voltage is highly process dependent: Vth=VFB - Qss/Cox + Vsub +2|Φp| + |Qd|/Cox

where:

VFB- flat band voltage,

Qss – surface charge per unit area,

Vsub – substrate voltage,

2| Φp| - voltage required for strong inversion, doping gradients

- Qd depletion charge per unit area in the depletion region

- Cox oxide capacitance per um2, depends on oxide thickness

All of them except Vsub are process dependent and randomly or graded distributed

Layout mismatch: Voltage drop on along power line can cause graded error

#### **Mismatches-History**

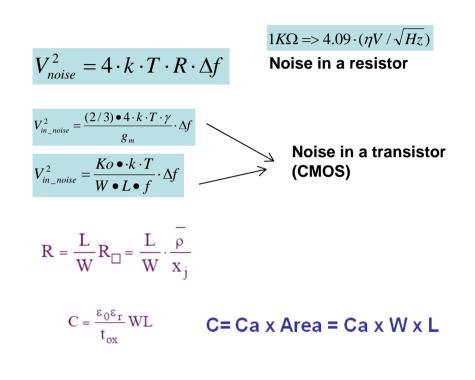

First belief was based on measured data : Very L dependent and Very W dependent

Low L Vt. goes down – so variations is large Low W Vt. goes up – so variation is large

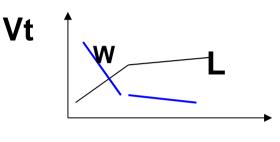

Today Pelgrom law define most mismatches as function of area WxL

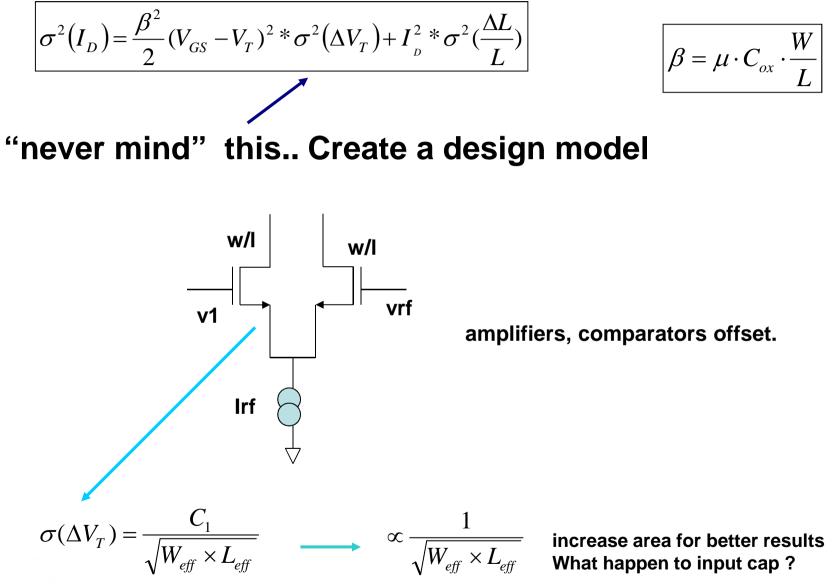

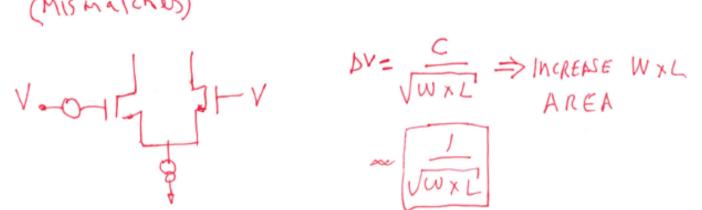

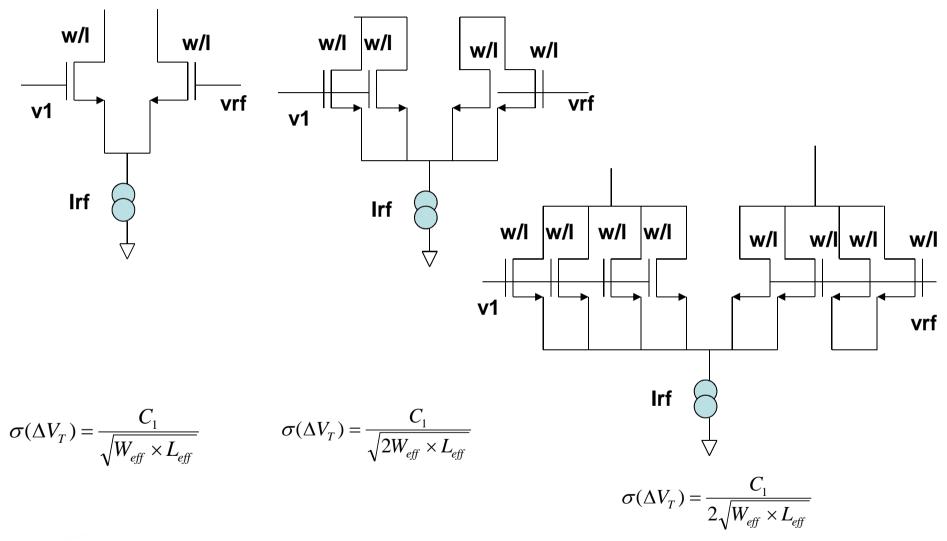

$$\sigma(\Delta V_T) = \frac{C_1}{\sqrt{W_{eff} \times L_{eff}}}$$

C1 is in today design ~ 2-10 mV for  $W \times L = 1 (u \times u)$

C1 has strong dependency on manufacturing – we do not have much control

C1 follow ~ 1.5 tox (in nm-> mv) as a "rule of thumb" – use thin oxide devices

C1 can be different for different layouts - we have control

Example for C1.

~ 3nm Tox --\_ 90nm process ~ 4.5mv x um 0.18um process tox=4nm ~ 6mv x um 3.3v process, tox~7nm ~ 10mv x um

### **V Mismatches- Saturation**

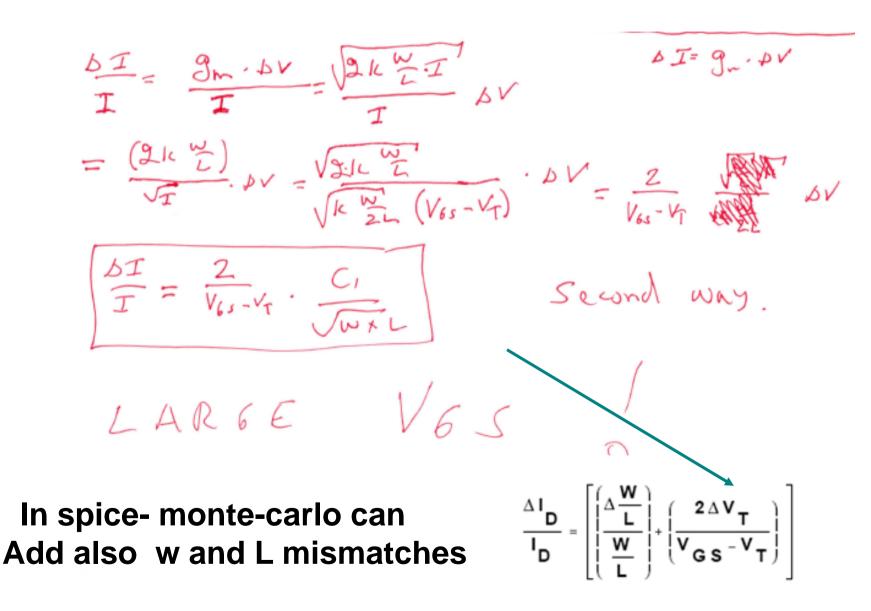

$$\begin{split} I &= k \frac{W}{2L} (V_{65} - V_{7})^{2} = d(V_{65} - V_{7})^{2} \\ bI + I &= k \frac{W}{2L} (V_{65} + \delta V - V_{7})^{2} = d(V_{65} - \delta V - V_{7})^{2} \\ P &= d(V_{65} - \delta V - V_{7})^{2} - (V_{65} - V_{7})^{2} \\ &= d(V_{65} - V_{7})^{2} + \delta V^{2} + 2(V_{65} - V_{7})^{2} \\ bI &= d (V_{65} - V_{7})^{2} + \delta V^{2} + 2(V_{65} - V_{7})^{4} \\ bI &= d (V_{65} - V_{7}) \\ \frac{\delta I}{I} &= d (V_{65} - V_{7})^{2} \\ &= d (V_{65} - V_{7})^{2} = Q \\ &= d (V_{65} - V_{7})^{2} - V_{15} - V_{15} \\ &= (\frac{2}{V_{65} - V_{7}}) \int W \times L \\ (\frac{\delta I}{I})^{2} &= (\frac{C}{V_{65} - V_{7}})^{2} \\ &= (\frac{C}{V_{65}$$

$$\frac{\sigma^2(I_{D})}{I_{D}^2} = \left\{\frac{\beta}{I_{D}}\sigma^2(\Delta V_{T}) + \sigma^2(\frac{\Delta L}{L})\right\} = \left\{\frac{2}{(V_{GS} - V_{T})^2}\sigma^2(\Delta V_{T}) + \sigma^2(\frac{\Delta L}{L})\right\}$$

#### **I Mismatches- Saturation- second method**

CURREN SOURCES MINIMIRE I offset, MISMATCH.

$$I = g_{M} \cdot DV = g_{M} C_{I} \cdot \left(\frac{k}{2} \times 2I\right) C_{I}$$

$N = DV = I + DI$ .

$DI = G = G = M + DV = U = U = U = U = U$

### Example: Mismatches/offset

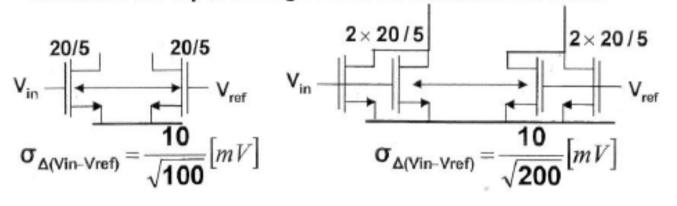

#### 4x transistor area = $\frac{1}{2}$ offset improvement

## **Calculate the Matching**

$$\sigma_{VT} = \frac{A_{VT}}{\sqrt{WL}} \quad A_{VT} = 10 \text{ mV} \mu \text{m}$$

V<sub>ref</sub> is fixed; Calculate the input-voltage-referred standard deviation

.

# **END** lecture 5a

www.gigalogchip.com

Technion 046188/2012

Lect 5a