Welcome to 046188 Winter semester 2012 <u>Mixed Signal Electronic Circuits</u> Instructor: Dr. M. Moyal

#### Lecture 04

Jitter and <u>Noise in Mixed Signal (Converters, and</u> <u>analog blocks).</u>

- 1. Jitter + few examples (summary lect1-3)

- 2. Noise sources in Mixed Signal

- 3. Passives elements in Silicon

www.gigalogchip.com

#### Quick-Summary lect. 2,3

| 0              |              |                   |

|----------------|--------------|-------------------|

| number of bits | S/N Accurate | S/N n 6.02 + 1.76 |

| n              | dB           | dB                |

| 1              | 6.31         | 7.78              |

| 2              | 13.30        | 13.80             |

| 3              | 19.52        | 19.82             |

| 4              | 25.59        | 25.84             |

| 5              | 31.65        | 31.86             |

| 6              | 37.70        | 37.88             |

| 7              | 43.76        | 43.90             |

| 8              | 49.82        | 49.92             |

| 9              | 55.87        | 55.94             |

| 10             | 61.93        | 61.96             |

Table 1.1: S/N as a function of the number of bits n

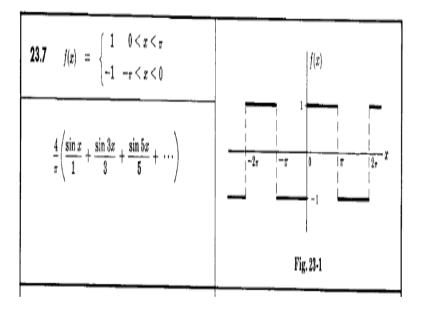

The signal-to-noise of an n-bit converter is accurately modeled with:

$$S/N(n) = \frac{A_1}{A_{quantization}} = \frac{2^{n-1} + \sum_{m=1}^{\infty} \frac{2}{m\pi} J_1(2m\pi 2^{n-1})}{\sqrt{\sum_{q=1}^{\infty} (\sum_{m=1}^{\infty} \frac{2}{m\pi} J_{2q+1}(2m\pi 2^{n-1}))^2}}$$

(1.45)

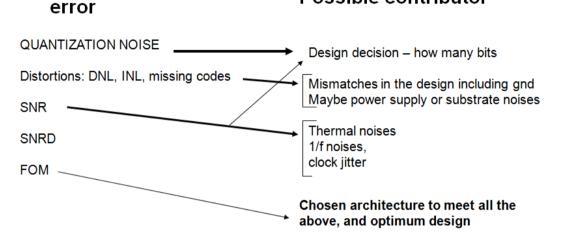

Possible contributor

DNL Definition Differences between two adjacent output digital or analog compared to a step size of LSB weight.

$$ENOBS(bit) \equiv SNDR(effec tive) - 1.76 / 6.02)$$

Industry "Accepted" Formula more correct for >3 bits..

#### In class derivation example..exact SNR 1-bit

# 6.28dB is the correct answer not 7.78

Example - 046188 O one metod  $\Delta = \frac{1}{2}, \frac{V_{FS}}{2^{n}} \Rightarrow \frac{2 \times \frac{1}{2}}{2^{1}} = (\frac{1}{2})$  $SURA = 20lg \frac{A^2}{V_2} OR 6.02h+1.76$   $\frac{A^2}{V_1}$  de = 6.02+1.76 = 7.78  $\frac{E \times A (1)}{P_{0}(S_{1})} = \frac{P_{0}(S_{1}) \times M(1)}{P_{0}(h \cup K \cdot L)} = \frac{P_{0}(S_{1}) \times M(1)}{P_{0}(h \cup K \cdot L)}$   $\frac{P_{0}(S_{1}) = FFT}{P_{0}(S_{1})} = FFT = FFT = FFT = FFT = FFT = FFT = FT =$

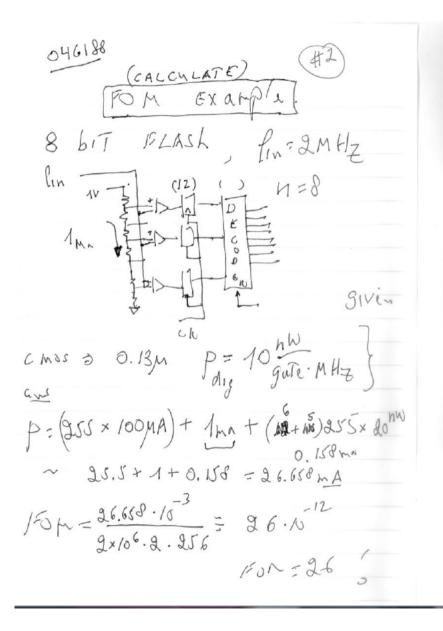

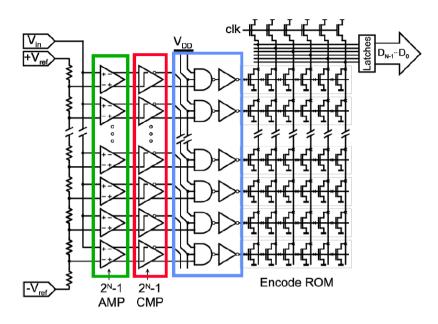

Step1:Inventory: rough est.

| 255 comparators, 255 resistors     |                |

|------------------------------------|----------------|

| 255 FFs                            | ~3 gates x 255 |

| Thermometer/binary nand+inv+8trans | ~3gates x 255  |

| Clock to comp ~ 5/line x 255       |                |

Key: MOSTLY COMP POWER Why 100Ua/COMP ?

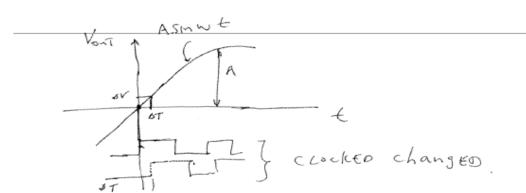

#### **CLOCK JITTER EFFECT IN CONVERTERS**

AT = JITTER

A = SIGNAL AMPLITUDE SNEWAVE =) ASMUE

SEARCH FOR MAX DV but

$$DV \leq 1LSB$$

$\frac{DV}{DT} = \frac{dV}{DT} = AW coswt = AW$

but  $2A = CUNVENTER RANGE = LSB = \frac{2A}{2^n}$

FIND EJITTE THAN HEVE COARSE TO GO OVER LSB

$$\frac{\delta V}{\delta T} = A W$$

$$\frac{\delta T}{mx} = \frac{2 S B \cdot 2}{W \cdot 9 n \cdot 2 S B} \frac{1}{T P_{in} \cdot 9 n}$$

$$\frac{\delta T}{mx} = \frac{1}{W \cdot 9 n \cdot 2 S B} = TT P_{in} \cdot 9 n$$

$$\frac{\delta T}{mx} = P tak T_{0} p tak C C b c k uncertainty$$

$$\frac{\delta T}{12} = \frac{1}{7 \cdot 7} \frac{1}{P S} \frac{1}{12} \frac{1}{9 \cdot 7} \frac{1}{19} \frac{1}{P S} \frac{1}{19} \frac{1}{$$

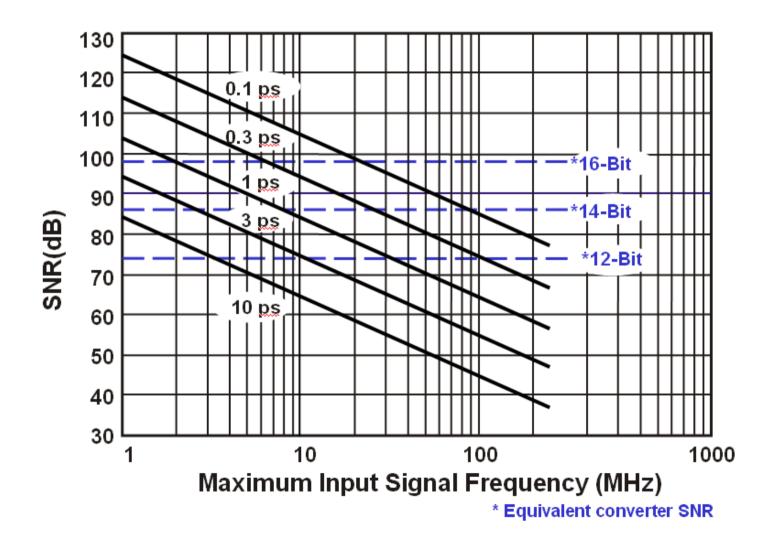

KEY: SNR due to jitter ifs input frequency dpepndent !

Technion 046188/2013

Ь

#### **Jitter Limits**

It is clear that the Clock effect is on high changing input (higer frequency..

But..

It is unclear where in the frequency lies this error ? Random ?

How does it correlate to Phase noise ?

Part of the project is to plot spectrum of the Jitter..

# Noise In Resistors and CMOS Transistors

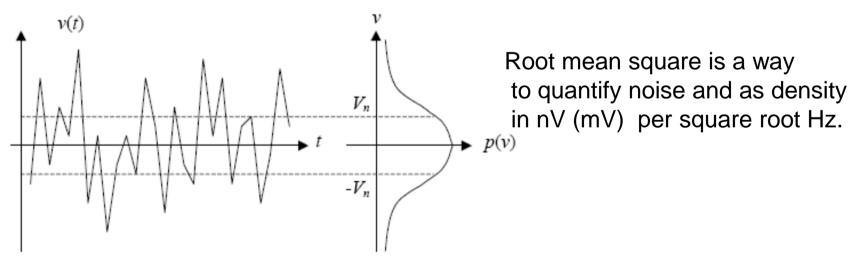

Noise set the fundamental limits of performance

Thermal energy in the device causes random charge carrier fluctuations, called thermal noise.

Thermal noise is considered a "white" noise source because its power spectral density (PSD) is independent of frequency up to about ft ( or the BW of the device).

We observe Voltage or Current noise of time and construct the PDF function

#### Source: T.H.Lee

# Example: A resistor thermal noise MODEL Vn R

#### Take KT=26mv x 1.6e-19C = 41.6 e-22 v square /ohm Hz **The model is a resistor with a voltage source 4KTR units are VxV/Hz**

Can Take the square root – noise density Sn)

$$V_{noise}^2 = 4 \cdot k \cdot T \cdot R \cdot \Delta f$$

$$1K\Omega => 4.09 \cdot (\eta V / \sqrt{Hz})$$

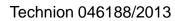

#### NOISE EFFECT IN CMOS TRANSISTORS

For MOS, We define 2 type of noises,

Two noise mechanism:

Thermal noise – white noise up to ft of the device Flicker noise – low frequency noise (not so low for Nmos)

It possible that in one mode or another 1/f is almost nulled

There exists other type of definitions for noise – Phase Noise, Electron Noise (ENC) Which are all derivatives or impacted from the basic Fliker and thermal noise (Mixing)

# Thermal noise: Thermal energy in the device causes random charge carrier fluctuations, called thermal noise.

Thermal noise is considered a "white" noise source because its power spectral density (PSD) is independent of frequency up to about ft ( or the BW of the device).

Flicker noise: results from random motion of charge over potential barrier (need a gate).

#### **Transistor Thermal and 1/f Noise**

Technion 046188/2013

Lect 04

#### **Noise and frequency**

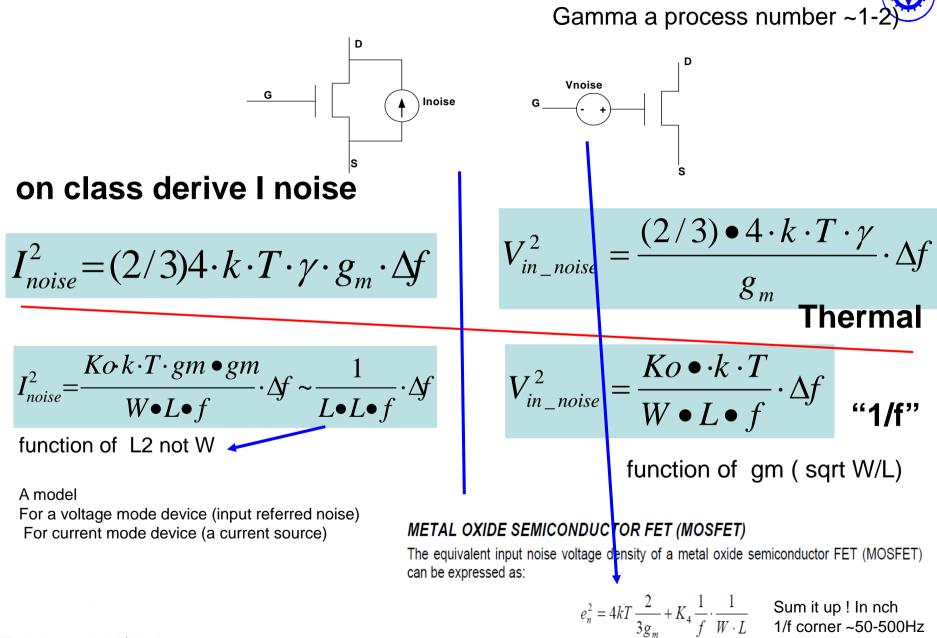

$$V_{in\_noise}^{2} = \frac{(2/3) \bullet 4 \cdot k \cdot T \cdot \gamma}{g_{m}} \cdot \Delta f$$

The total noise (input referred) is always the area under the density noise curve the integral from f=0 to f="your design system uses"-hard to tell

#### as voltage mode:

Thermal noise: Vn2 /del f = 8 KT/3 gm use large w/l and gm  $\rightarrow$  lower noise

1/f noise Vn2 /del f = Ko KT / f W L use large area W XL  $\rightarrow$  lower noise

Drain current noise

$In^{2} /del f = 8 KT gm/3 \qquad \text{function of gm} (sqrt W/L)$  $In^{2} /del f = Ko KT gm^{2} / f W L \qquad \text{function of } L^{2} not W$

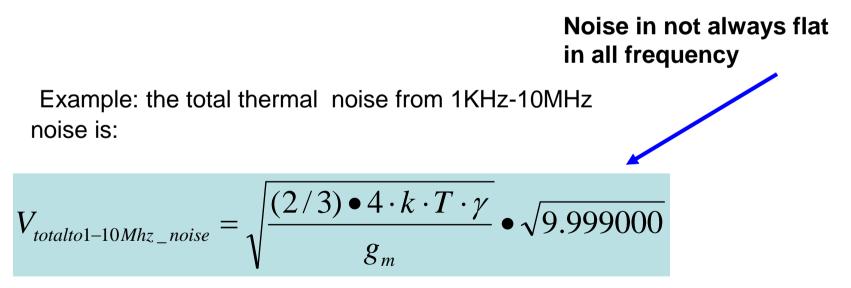

#### Example 1ckt noise of 2 gain stages – in class

Inz In - gnp. DV ToTAL "Input" hoist  $V_{M1}^{2} + \frac{T_{N2}}{g_{M1}^{2}} + \frac{V_{R}^{2} + V_{N3}}{g_{M1}^{2} \cdot (R_{o_{M1}} || k_{o_{M2}})^{2}}$  $V = \frac{8}{3} \frac{1cT}{8HI} + \frac{8}{3} \frac{1cT}{9HP} + \frac{41cTR + \frac{8}{3} \frac{1cT}{9H3}}{\frac{9H3}{3}} + \frac{41cTR + \frac{8}{3} \frac{1cT}{9H3}}{\frac{9H3}{3}}$ LARGA (3 + SMELL Melle grout WI Lt Males grop - Low + = FOR ADG ful 2458 - 1 12 (BW)

#### **Passive RC in Silicon**

# and **MISMATCHES**

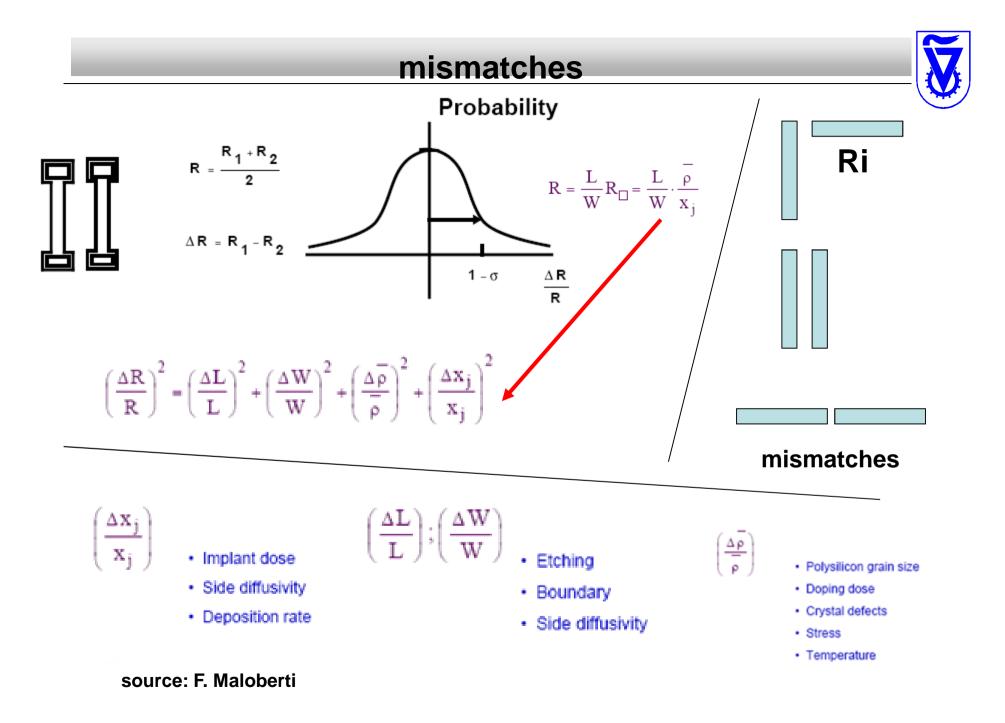

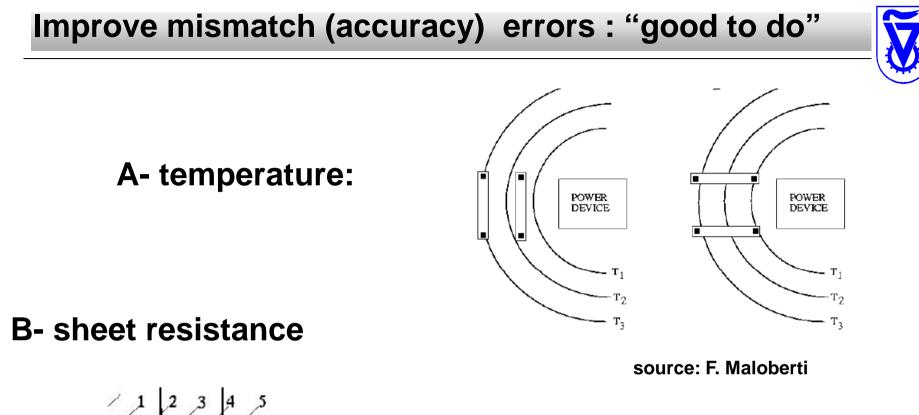

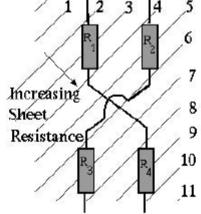

Mismatches

One of the most critical parameters in Mixes signal design.

Mostly ignored with normal simulators

#### Si passive Elements Used in Mixed Signal

Silicon Resistors:

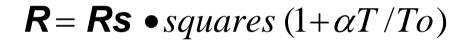

In Silicon  $\mathbf{R}$  = Sheet resistance x Number of square. Made of Si doped material.( poly and N+ or P+ or both.)

Problems: They have parasitic capacitances, (BW limitation) and Temperature variations :

$R \propto 1/(\mu q N a)$

Lect 04

# Polysilicon

Grown from pyrolytic decomposition of silane (SiH<sub>4</sub>) at about 600°C.

The polycrystalline structure is made of monocrystal grains size in the range of 0.1 - 1  $\mu m.$

The typical layer are 200 - 600 nm thick with long term standard deviation in the 2% range.

The mobility is low because of the grain border resistance (30-40 cm<sup>2</sup>/Vs).

In order to have a low sheet resistance the polysilicon must be strongly doped ( $10^{20}-10^{21}$  cm<sup>-3</sup>). Part of the doping saturates the localized levels due to the grain border. The sheet resistance is in the range 20 - 40  $\Omega/\Box$ .

The sheet resistance can be reduced by using sandwich layers (polysilicide) made of 200 nm of polysilicon covered with a film of refractory metal silicide (WSi<sub>2</sub>, MoSi<sub>2</sub>, TiSi<sub>2</sub>). The sheet resistance is reduced to 1 - 5  $\Omega/\Box$ .

#### **Common type of resistors in IC - silicon**

| RESISTOR                             | Range   | 0hm/sq<br>Value | % (1x1uu)<br>matching | ppm/c ,ppm/v<br>temco |

|--------------------------------------|---------|-----------------|-----------------------|-----------------------|

| Poly<br>No siliside<br>With siliside | +/-15%  | 200-1k<br>6     | 2%<br>-               | 0-400 ppm/c<br>-      |

| N+/P+                                | +/-20%  | 20-100          |                       | 3000ppm/c, large v.   |

| N well                               | +/- 20% | 2k-4k           |                       | large                 |

| 1 Contact                            | +/- 50% | 1-3 ohm         |                       |                       |

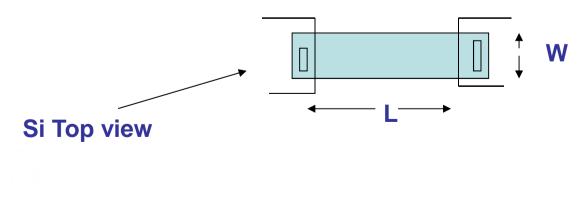

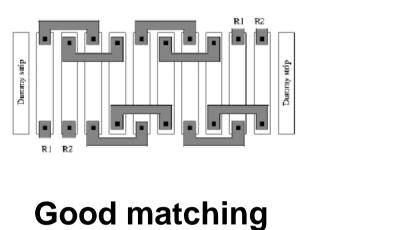

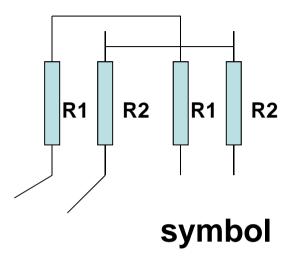

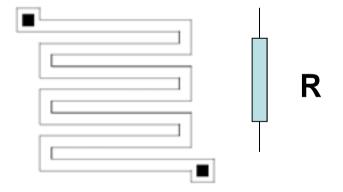

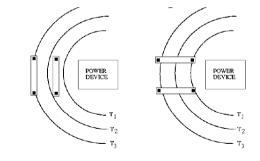

#### Layout of resistors in silicon

#### Interdigitized structure :

**R**=**Rs**•*length/width*

**Rtotal** = **R**+0.5*Rs*(*numberturns*)+

+ Contact resistance

"James C. Daly et al."

C) STRESS: away from edges..

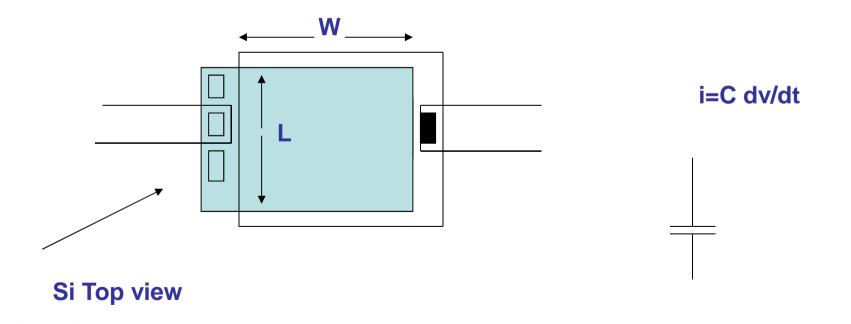

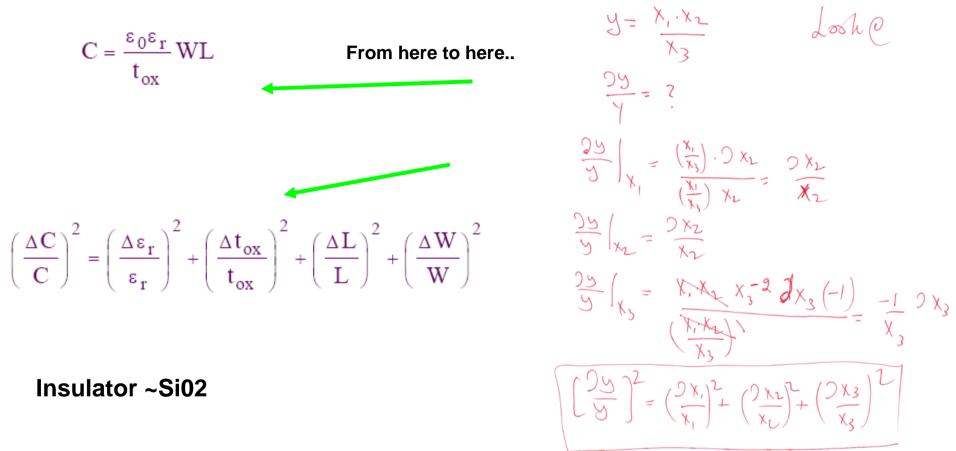

# Capacitors

#### **Plated Capacitors**

**C= Ca x Area = Ca x W x L** (W and L are dimension of plates) 1-4 ff/uu can. 20pF is already a large capacitors for Si application.

"Core Oxide caps"- will be reviewed later lectures.

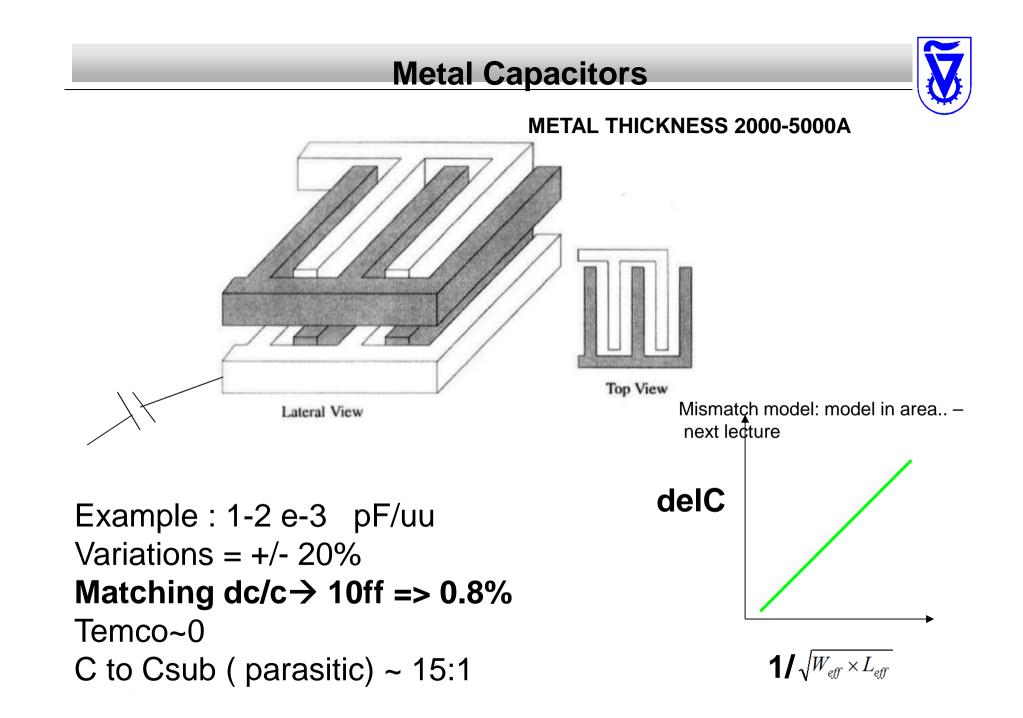

#### Capacitors

Mismatch model: know, but ignore the above use pelgrom rule ! Given mismatch for certain area everything and 4 time the area means double the matching- next lecture...

### END lecture 04

www.gigalogchip.com