Welcome to 7718 semester 1 2022 <u>Mixed Signal Electronic Circuits</u>

Instructor: Dr. Miki Moyal

Lecture 02

Noise, and mismatches in Mixed Signal

1.Basic circuit examples, and assignment 12.Noise3.Mismatche

Lectures http://www.gigalogchip.com/lectures.html

#### Last lecture summary

November 4, 2022

Semester / 1

I put in the site..

Few words..

The CTLE

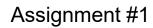

Difference between Vinp=-vinn

and 2vinn, 0

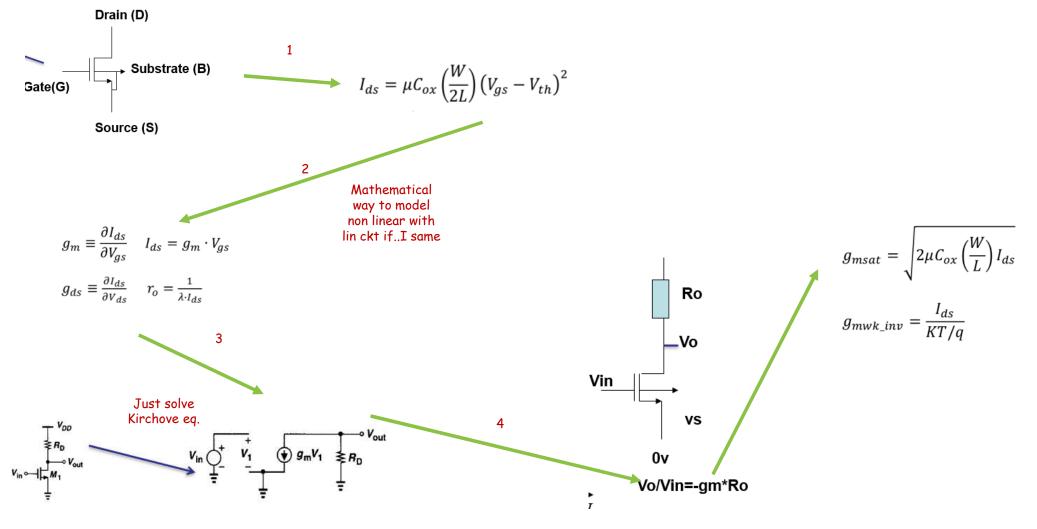

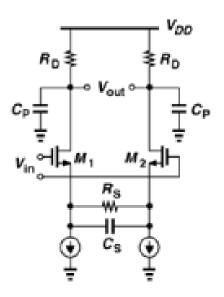

#### Few important analog circuits: basic in class analysis

#### optional

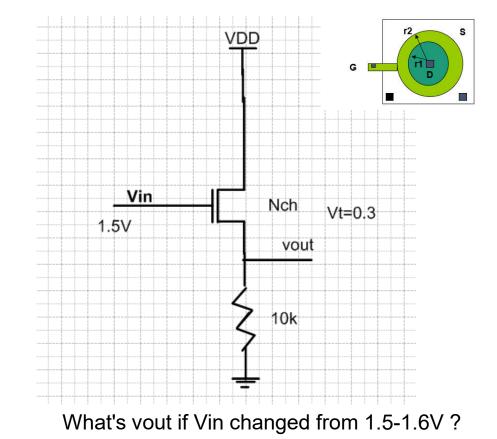

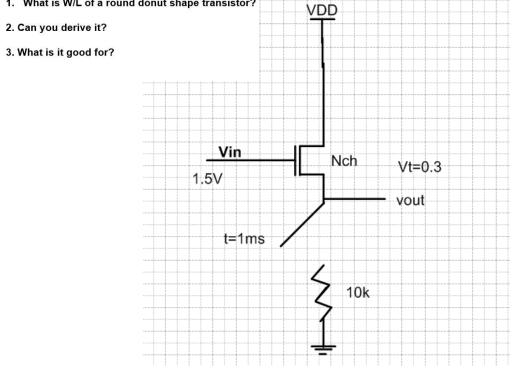

- 1. What is W/L of a round donut shape transistor?

- 3. What is it good for?

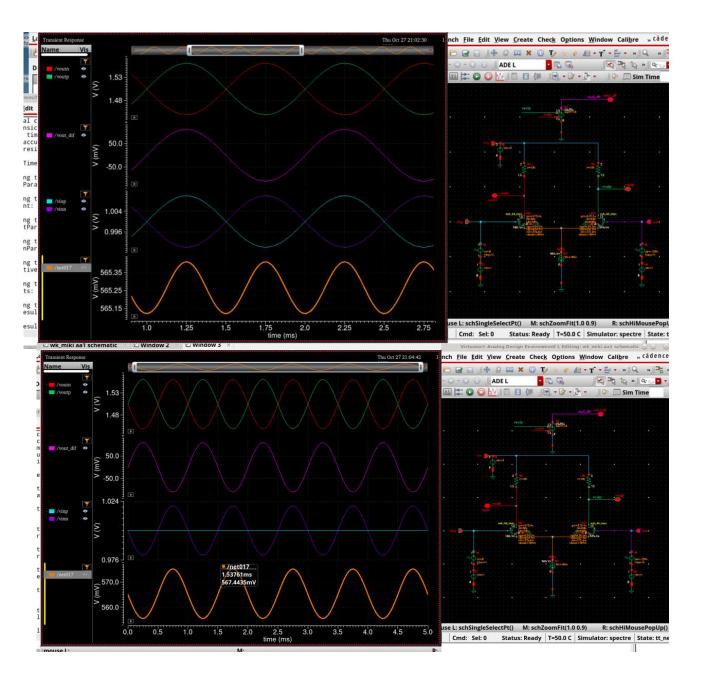

What's vout after long time ? 1Hr.

# Time for noise...

# Noise In resistors and CMOS transistors

#### Noise set the fundamental limits of performance

#### **Impact of Noise**

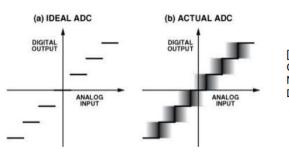

[W. Kester, "ADC Input Noise: The Good, The Bad, and The Ugly. Is No Noise Good Noise?" Analogue Dialogue, Feb. 2006]

- In essentially all moderate to high-resolution ADCs, the transition levels carry noise that is somewhat comparable to the size of an LSB

- Noise "smears out" DNL, can hide missing codes

- Especially for converters whose input referred (thermal) noise is larger than an LSB, DNL is a "fairly useless" metric

12

Basics of Noise- "In time"

- □ Thermal energy in the device causes random charge carrier fluctuations, called Thermal Noise.

- Thermal Noise is considered a "white" noise source because its Power Spectral Density (PSD) is independent of frequency up to about f<sub>t</sub> (or the BW of the device).

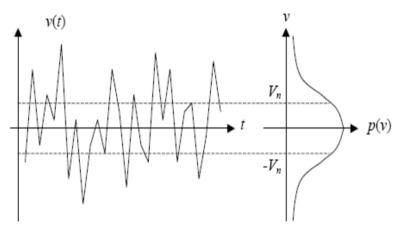

we observe Voltage or Current noise in time and construct the PDF function

Root mean square is a way to quantify noise and as density in nV (mV) per square root Hz.

#### Source: T.H.Lee

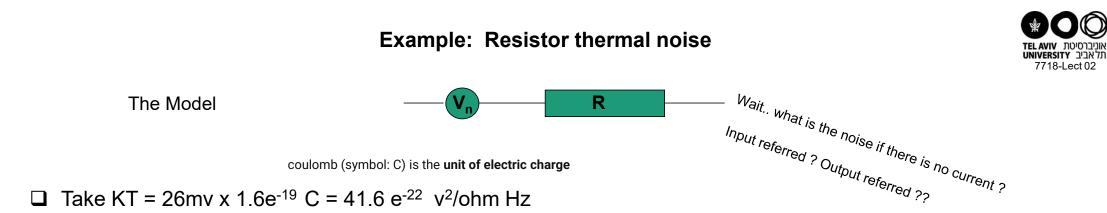

#### □ The model is a resistor with a voltage source of 4KTR units are V<sup>2</sup>/Hz

Can Take the square root – noise density Sn)

$$V_{\rm T} = \frac{kT}{q} = \frac{1.38 \times 10^{-23} \text{ J} \cdot \text{K}^{-1} \times 300 \text{ K}}{1.6 \times 10^{-19} \text{ C}} \simeq 25.85 \text{ mV}$$

$$V_{noise}^2 = 4 \cdot k \cdot T \cdot R \cdot \Delta f$$

$$1K\Omega \gg 4.09(\frac{nV}{\sqrt{Hz}})$$

can think the Vnoise is \*\*rms voltage\*\*( its in a "bin", density)

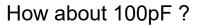

In class example TIA

Willy Sansen 10-05 046

Semester / 1

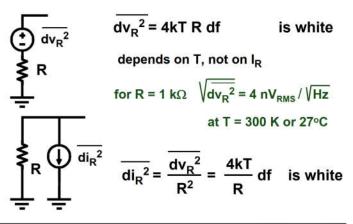

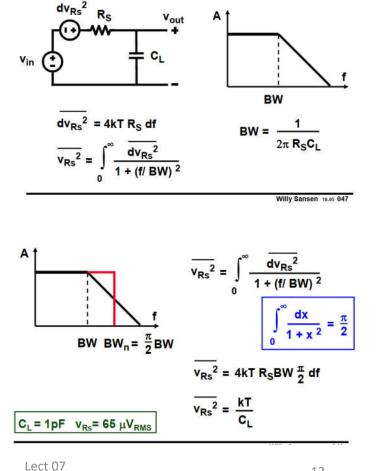

Noise versus frequency

Willy Sansen 10-05 045

I always take the density and multiply by the squar root of the freqency rang: for 100Hz-10M = squre root of(10,00000-100)

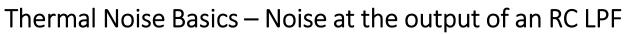

Next: what if we have a filter ?

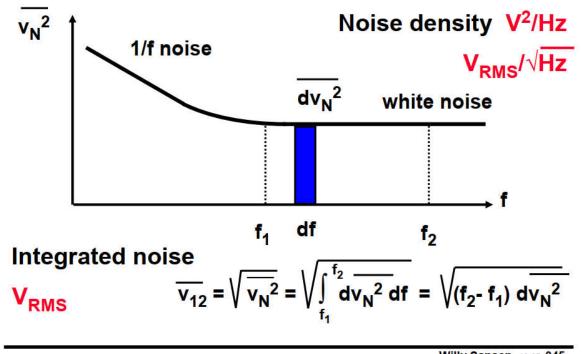

The thermal noise of a resistor is given by:

$$Vn_R^2(f) = 4kTR$$

The noise equivalent circuit of an RC LPF is:

We can now calculate the output noise power as:

$$\overline{Vn_{out}^2} = Vn_R^2(0) \cdot BWR = 4kTR\frac{\pi}{2}f_p = 4kTR\frac{\pi}{2}\cdot\frac{1}{2\pi RC} = \frac{kT}{C}$$

The noise charge on the capacitor has the variance:

$$\overline{Qn^2} = \overline{Vn^2} \cdot C^2 = kTC$$

November 4, 2022

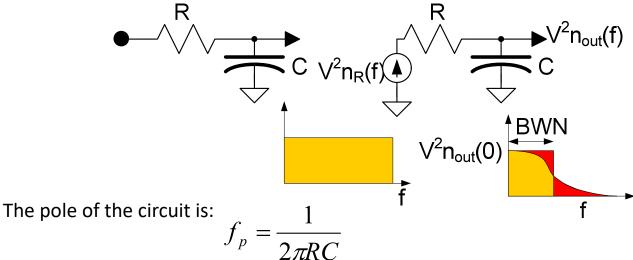

Integrated Noise of Resistor - 1

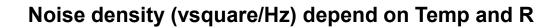

Summary noise in R

Total noise Vrms=(integrated) depend on Temp and 1/C

$$Vn_R^2(f) = 4kTR$$

$$\overline{\mathbf{v}_{Rs}^2} = \frac{kT}{C_L}$$

In class example TIA

# Noise in CMOS transistors

□ For MOS, We define 2 type of noises:

Thermal Noise – White noise up to f<sub>t</sub> of the device

Flicker Noise – Low frequency noise (1/f, not so low for NMOS)

It possible that in one mode or another 1/f is almost nulled

In later lecture we will see that other type of definitions for noises – Phase Noise, Electron Noise (ENC), which are all derivatives or impacted from the basic Flicker and Thermal noise (Mixing)

#### Thermal noise and Flicker noise

#### □ Thermal noise:

□ Thermal energy in the device causes random charge carrier fluctuations, called Thermal noise.

□ Flicker noise:

Results from random motion of charge over potential barrier (need a gate).

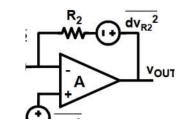

# Noise of a diode is shot noise

for

$$I_D = 50 \ \mu A \ \sqrt{di_D^2} = 4 \ pA_{RMS} / \sqrt{Hz}$$

Willy Sansen 10-05 0411

November 1, 2022

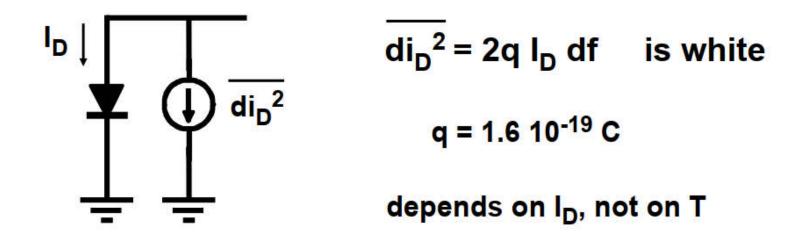

#### **Transistor Thermal and 1/f Noise**

Models:

For a *Voltage* Mode device (input referred noise)

For a *Current* Mode device (a current source)

7718-Lect 02

#### Noise and frequency

□ The total noise (input referred) is always the area under the density noise curve the integral from f=0 to f="what you like"

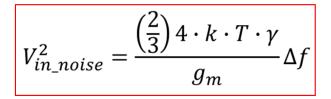

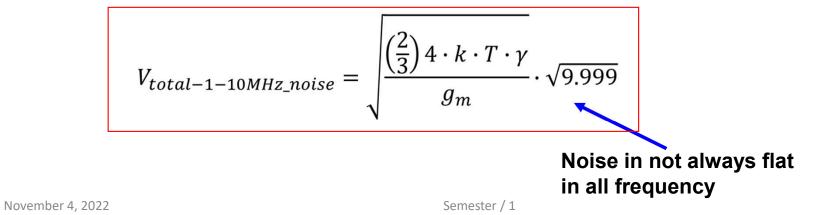

Example: the total thermal noise from 1KHz-10MHz noise is:

Voltage Mode:

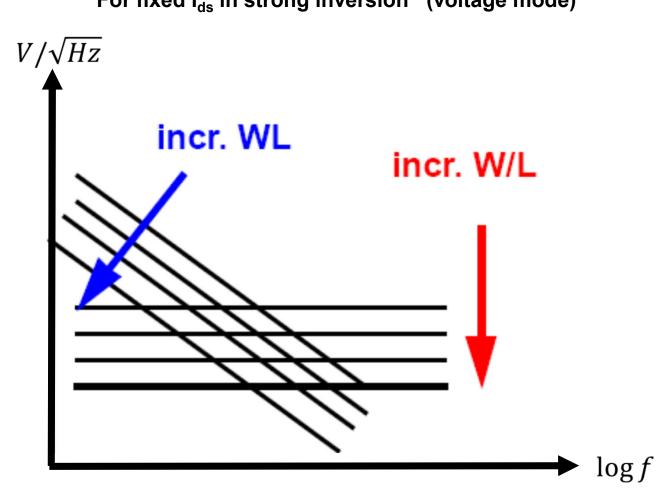

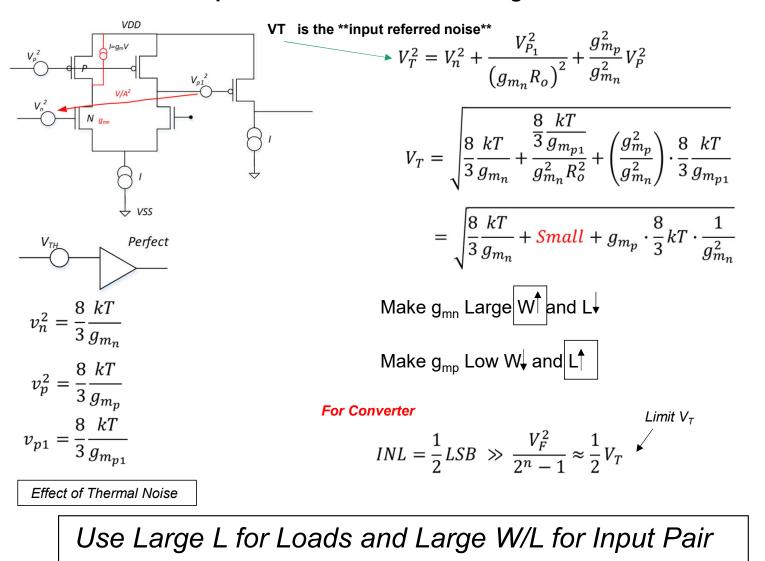

Thermal noise:  $\frac{V_n^2}{\Delta f} = \frac{8KT}{3g_m}$  $g_m = \sqrt{2\mu C_{ox} \frac{W}{L} I_{ds}}$ use <u>Large</u> W/L  $(g_m) \rightarrow$  for low noise But it could be a loosing game spend a lot of gm to reduce the noise a little..  $\Box$  1/f noise:  $\frac{V_n^2}{\Delta f} = \frac{K_0 KT}{fWL}$ use Large area WxL  $\rightarrow$  Lower noise Why?landC Drain Current Mode:  $\frac{I_n^2}{\Delta f} = \frac{8KTg_m}{3}$  Function of g<sub>m</sub> (sqrt W/L)  $\frac{I_n^2}{\Delta f} = \frac{K_0 KT g_m^2}{fWL}$  Function of L<sup>2</sup> not W

November 4, 2022

Semester / 1

# For fixed $I_{ds}$ in strong inversion (voltage mode)

Flicker and thermal noises Interactions

the text of the text of the text of the text of text of the text of t

#### Example circuit noise of 2 Gain Stages On Board

November 4, 2022

Semester / 1

7718-Lect 02

# **Mismatch**

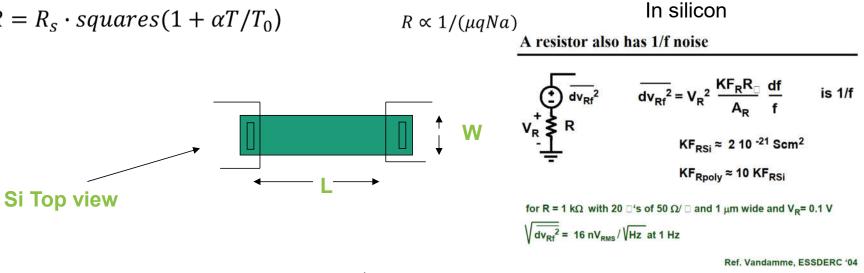

## Passives: resistors and capacitors in silicon

- □ One of the most critical parameters in mixes signal design.

- □ Mostly ignored with normal simulators

#### Polysilicon

#### Silicon Passive elements used in Mixed Signal

Silicon Resistors: R=v/i

□ In Silicon

R = Sheet Resistance x Number of square.

Made of Si doped material.(poly and N+ or P+ or both)

#### □ Problems:

They have parasitic capacitances, (BW limitation) and temperature variations :

$$R = R_s \cdot squares(1 + \alpha T/T_0)$$

Grown from pyrolytic decomposition of silane (SiH₄) at about 600°C.

The polycrystalline structure is made of monocrystal grains size in the range of 0.1 - 1 µm.

The typical layer are 200 - 600 nm thick with long term standard deviation in the 2% range.

The mobility is low because of the grain border resistance (30-40 cm<sup>2</sup>/Vs).

In order to have a low sheet resistance the polysilicon must be strongly doped (10<sup>20</sup>-10<sup>21</sup> cm<sup>-3</sup>). Part of the doping saturates the localized levels due to the grain border. The sheet resistance is in the range 20 - 40  $\Omega/\Box$ .

The sheet resistance can be reduced by using sandwich layers (polysilicide) made of 200 nm of polysilicon covered with a film of refractory metal silicide (WSi<sub>2</sub>, MoSi<sub>2</sub>, TiSi<sub>2</sub>). The sheet resistance is reduced to 1 - 5  $\Omega/\Box$ .

24

**Passive Element Tolerance**

# □ Common type of resistors in IC - silicon

| Resistor                              | Range [%] | Ohm/sq<br>Value | Matching<br>[%]<br>(1x1uu) | ppm/c, ppm/v        |

|---------------------------------------|-----------|-----------------|----------------------------|---------------------|

| Poly<br>W/O Siliside<br>With Siliside | ± 15      | 200 – 1k<br>6   | 2                          | 0-400 ppm/c<br>-    |

| N+/P+                                 | $\pm 20$  | 20-100          | -                          | 3000 ppm/c, large v |

| N well                                | $\pm 20$  | 2k-4k           |                            | Large               |

| 1 contact                             | $\pm 50$  | 1-3             |                            |                     |

#### Tolerance is not mismatch...

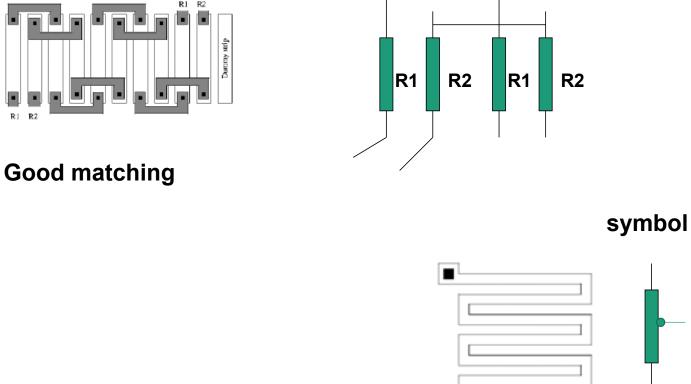

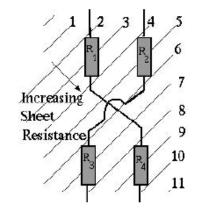

#### Layout of resistors on Silicon

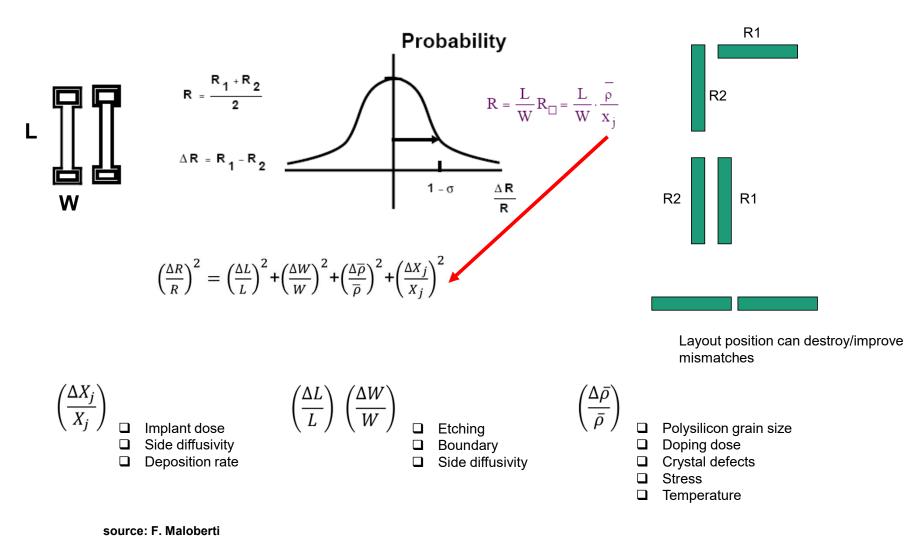

$R = R_s \cdot length/width$

Interdigitized structure :

Denny ship

$R_{total} = R + 0.5 \cdot R_s(number_{turns}) + contact_resistance$

R

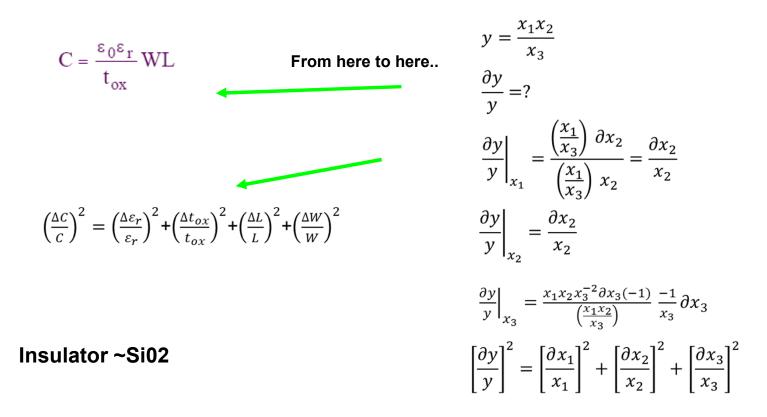

#### **Basic partial derivatives**

$$y = \frac{x_1 x_2}{x_3}$$

$$\frac{\partial y}{y} = ?$$

$$\frac{\partial y}{y}\Big|_{x_1} = \frac{\left(\frac{x_1}{x_3}\right) \partial x_2}{\left(\frac{x_1}{x_3}\right) x_2} = \frac{\partial x_2}{x_2}$$

$$\frac{\partial y}{y}\Big|_{x_2} = \frac{\partial x_2}{x_2}$$

$$\frac{\partial y}{y}\Big|_{x_3} = \frac{x_1 x_2 x_3^{-2} \partial x_3(-1)}{\left(\frac{x_1 x_2}{x_3}\right)} \frac{-1}{x_3} \partial x_3$$

$$\left[\frac{\partial y}{y}\right]^2 = \left[\frac{\partial x_1}{x_1}\right]^2 + \left[\frac{\partial x_2}{x_2}\right]^2 + \left[\frac{\partial x_3}{x_3}\right]^2$$

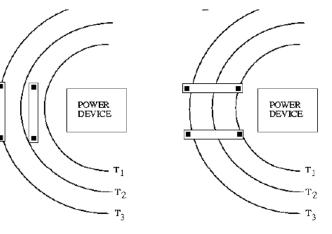

#### **Mismatches**

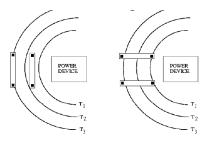

Improve Mismatch (Accuracy) Errors : "Good to Do"

**B** – Sheet resistance

source: F. Maloberti

### C – Stress: away from edges..

"James C. Daly et al."

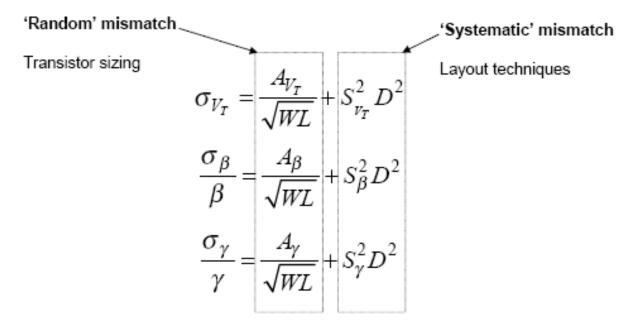

#### Mismatches – Modelling – "Pelgrom Rule"

#### MISMATCHING In Current-Steering D/A Converters

M.J.M Pelgrom, et al (1989): mismatching parameter for two equal transistor of dimensions W x L separated a distance D.

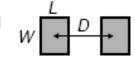

#### **Capacitors layout and mismatched**

#### **Plated Capacitors**

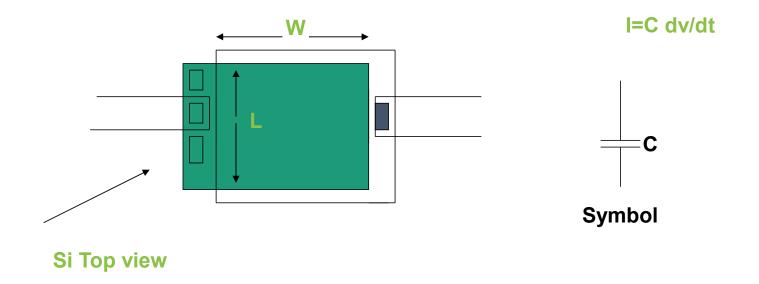

C= Ca x Area = Ca x W x L (W and L are dimension of plates)

1-4 ff/uu, 20pF is already a large capacitors for silicon application.

"Core Oxide caps"- will be reviewed later lectures.

#### Capacitors

- □ Mismatch model: should know but **ignore the above and use pelgrom rule !**

- Given mismatch for certain area everything and 4 time the area means double the matching

# **Metal capacitors** 7718-Lect 02 Metal thickness ~ 2000-5000A (A=Angstrom) Top View Csub ΔC Lateral View Example : $C= 2 e^{-3} pF/uu$ Variations = +/-20%If for a Given 2ff=2% mismatch - process number. Then for a 100ff capacitor we will ger Matching dc/c $\rightarrow$ 100ff => 2/7 = 0.28% More parameters: Temco~0 C to $C_{sub}$ (parasitic) ~ 10:1 $\rightarrow$ 30:1 Variations = +/- 20% $1/\sqrt{W_{eff}xL_{eff}}$

Noise = 192uV..

#### In reality we characterize a process capacitor and resistors in silicon mismatch as

Smallest 1 square = x%from than on we can deduce the mismatch to any value

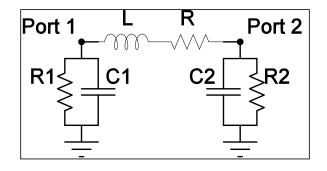

#### **Inductors**

Inductors are also becoming a common elements- we will not go over the detail of inductor design in this course ( only the basics once we go over PLLs lecture)

$$L_{self} = \frac{\mu_0}{2\pi} \left[ l \ln \left( \frac{2l}{w+t} \right) + \frac{l}{2} + 0.2235(w+t) \right] (1)$$

Source: Stanford, synopsys, and HP paper on L modelling

Semester / 1

#### **Mismatches in transistors**

First test:

Is it a current source mode?

Is it a voltage mode device?

Is it a switch?

Mixed signal design must address:

Can we live with that?If not can we "calibrate" or fix this error?

#### Mismatches- V<sub>th</sub>.

Process deviation:

Threshold voltage is highly process dependent: Vth=VFB - Qss/Cox + Vsub +2|Φp| + |Qd|/Cox,

$$V_{th} = V_{FB} - \frac{Q_{ss}}{C_{ox}} + V_{sub} + 2|\phi_p| + \frac{|Q_d|}{C_{ox}}$$

Where:

- V<sub>FB</sub> Flat Band Voltage,

- Q<sub>ss</sub> Surface Charge per unit area,

V<sub>sub</sub> - Substrate Voltage,

- $2_{|\Phi p|}$  Voltage required for strong inversion, doping gradients

- $Q_d$  Depletion charge per unit area in the depletion region

- Cox Oxide Capacitance per um2, depends on oxide thickness

- All of them except V<sub>sub</sub> are process dependent and randomly or graded distributed

- Layout mismatch: Voltage drop on along power line can cause graded error

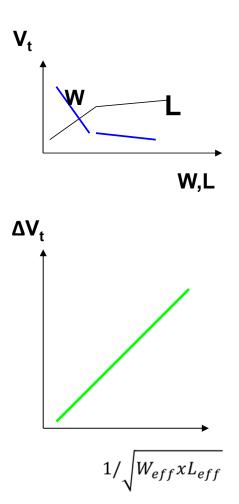

#### **Mismatches-history**

First belief was based on measured data:

Very L dependent and Very W dependent

Low L Vt. goes down – so variations is large

Low W Vt. goes up – so variation is large

- Today Pelgrom law define most mismatches as function of area WxL

- And simulators namely monte carlo do the job of finding the sigma mismatch of large blocks

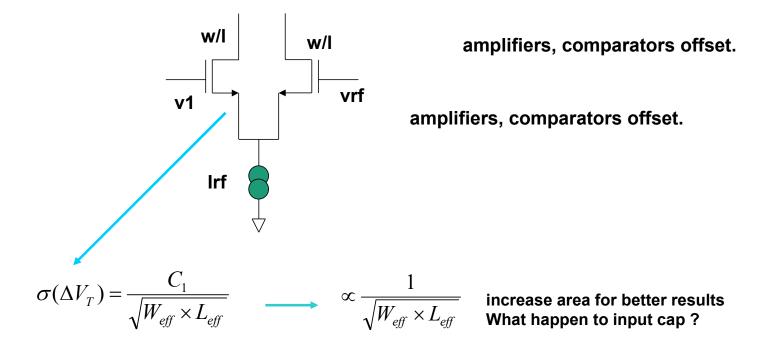

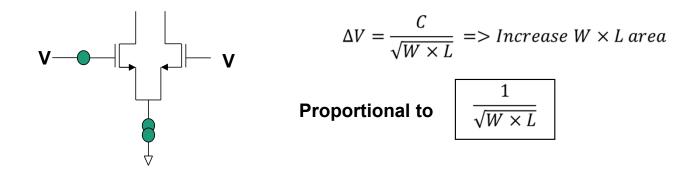

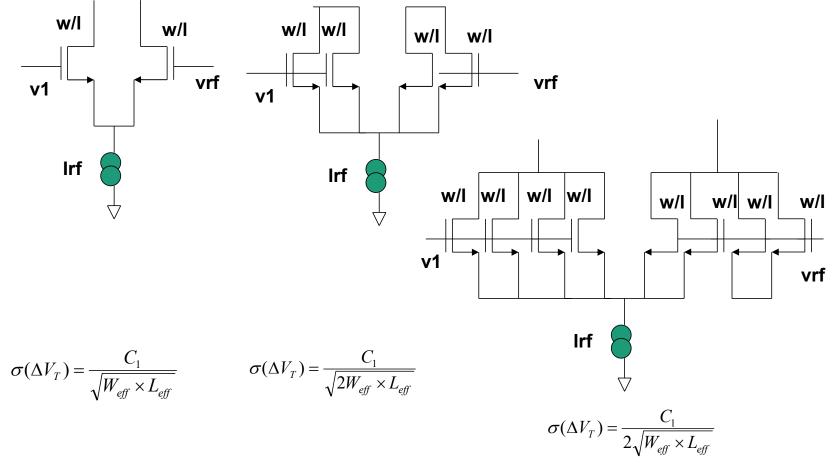

$$\sigma(\Delta V_T) = \frac{C_1}{\sqrt{W_{eff} \times L_{eff}}}$$

#### Note on C1 from last page

- □ C1 is in today design 2-10 mV for W x L =1

- □ C1 has a strong dependency on manufacturing we do not have much control

- $\Box$  C1 follow ~ 1.5 t<sub>ox</sub> (in nm -> mv) as a "rule of thumb" use thin oxide devices

- □ C1 can be different for different layouts we have control

Example for C1.

~ 3nm tox -- 90nm process ~ 4.5mv um 0.18um process tox=4nm ~ 6mv x um 3.3v process, tox~7nm ~ 10mv x um

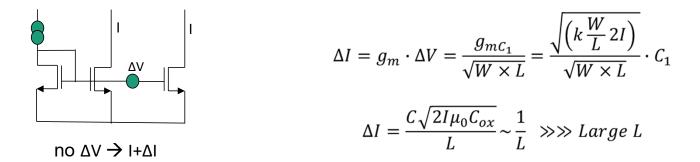

#### V Mismatches – saturation region

"never mind" this.. create a design model

**|**+∆I

ΔV

$\checkmark$

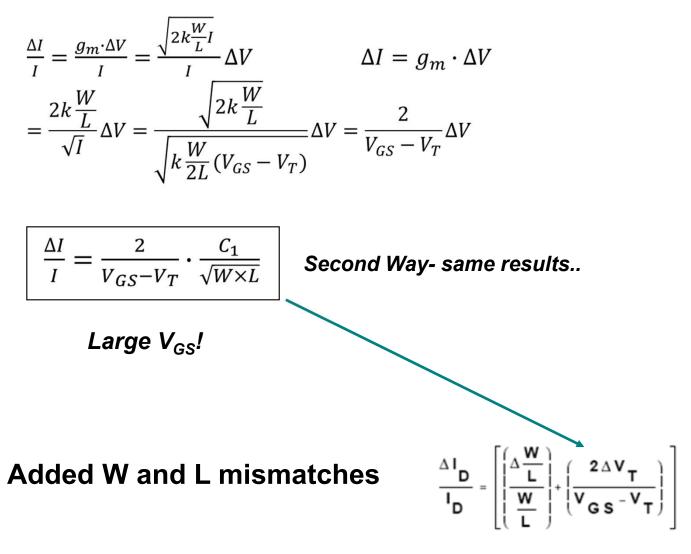

#### **Current mismatches in saturation – first method**

$$I = k \frac{W}{2L} (V_{GS} - V_T)^2 = \alpha (V_{GS} - V_T)^2$$

$$\Delta I + I = k \frac{W}{2L} (V_{GS} + \Delta V - V_T)^2 = \alpha (V_{GS} - \Delta V - V_T)^2$$

$$\Delta I = \alpha [(V_{GS} - \Delta V - V_T)^2 - (V_{GS} - V_T)^2]$$

$$= \alpha [(V_{GS} - V_T)^2 + \Delta V^2 + 2(V_{GS} - V_T)\Delta V - (V_{GS} - V_T)^2]$$

$$\Delta I = \alpha \cdot 2(V_{GS} - V_T)$$

$$\frac{\Delta I}{I} = \frac{\alpha \cdot 2(V_{GS} - V_T)\Delta V}{\alpha (V_{GS} - V_T)^2} = \frac{2}{V_{GS} - V_T} \cdot \Delta V = \left[\frac{2}{V_{GS} - V_T}\right] \cdot \frac{\sigma_{(V_T)}}{\sqrt{W \times L}}$$

$$\left(\frac{\Delta I}{I}\right)^2 = \left(\frac{C_1}{\sqrt{W \times L}}\right)^2 \frac{4}{(V_{GS} - V_T)^2}$$

**One Way**

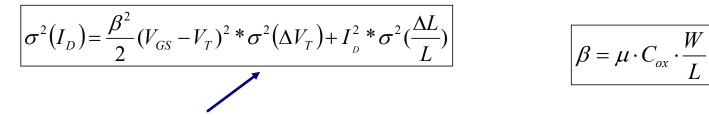

$$\frac{\sigma^2(I_D)}{I_D^2} = \left\{\frac{\beta}{I_D}\sigma^2(\Delta V_T) + \sigma^2(\frac{\Delta L}{L})\right\} = \left\{\frac{2}{(V_{GS} - V_T)^2}\sigma^2(\Delta V_T) + \sigma^2(\frac{\Delta L}{L})\right\}$$

Semester / 1

#### **Current** mismatches in saturation – second method use C1

#### Mismatches/Offset V<sub>s</sub>, L, W,

Amplifiers, comparators minimize Offset (mismatches)

Current source minimize I Offset Mismatch

#### Example: mismatches/Offset

4x transistor area =  $\frac{1}{2}$  offset improvement

Semester / 1

# End of lecture 02